2022江西紡織服裝周暨江西(贛州)紡織服裝產業博覽會隆重舉行

為深入學習貫徹落實黨的二十大和二十屆一中...

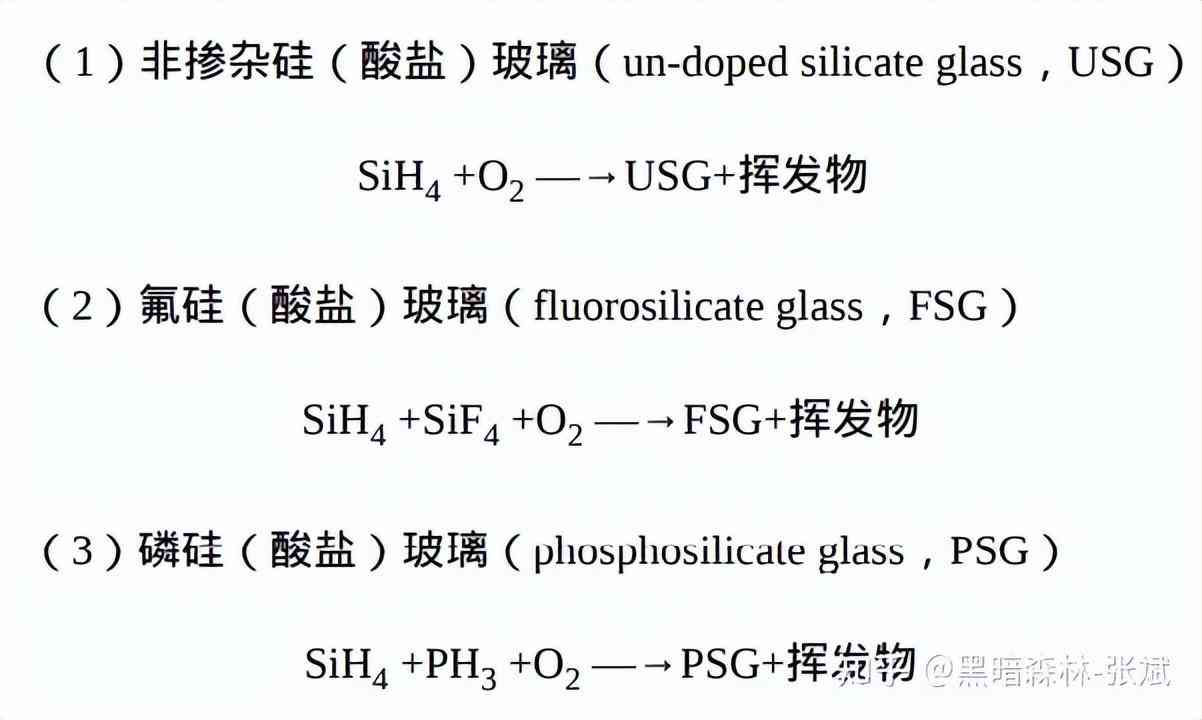

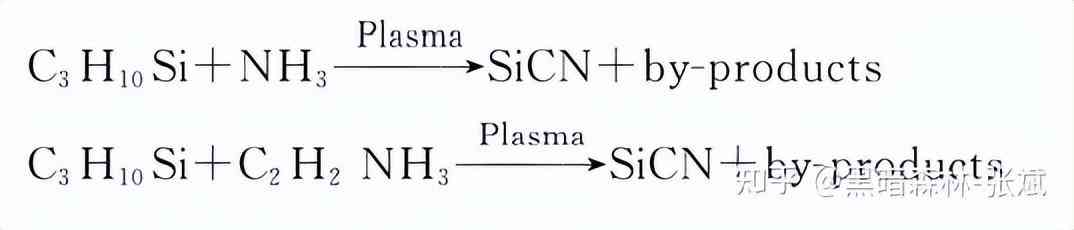

電介質在集成電路中主要提供器件、柵極和金屬互連間的絕緣, 選擇的材料主要是氧化硅和氮化硅等,沉積方法主要是化學氣相沉積(CVD)。隨著技術節點的不斷演進,目前主流產品已經進入65/45nm的世代,32/28nm產品的技術也已經出現,為了應對先進制程帶來的挑戰,電介質薄膜必須不斷引入新的材料和新的工藝。

電介質是能夠被電極化的絕緣體。 電介質的帶電粒子是被原子、 分子的內力或分子間的力緊密束縛著, 因此這些粒子的電荷為束縛電荷。 在外電場作用下, 這些電荷也只能在微觀范圍內移動, 產生極化。 在靜電場中, 電介質內部可以存在電場, 這是電介質與導體的基本區別。

在電磁學里,當給電介質施加一個電場時,由于電介質內部正負電荷的相對位移,會產生電偶極子,這現象稱為電極化。施加的電場可能是外電場,也可能是嵌入電介質內部的自由電荷所產生的電場。因為電極化而產生的電偶極子稱為“感應電偶極子”,其電偶極矩稱為“感應電偶極矩”。

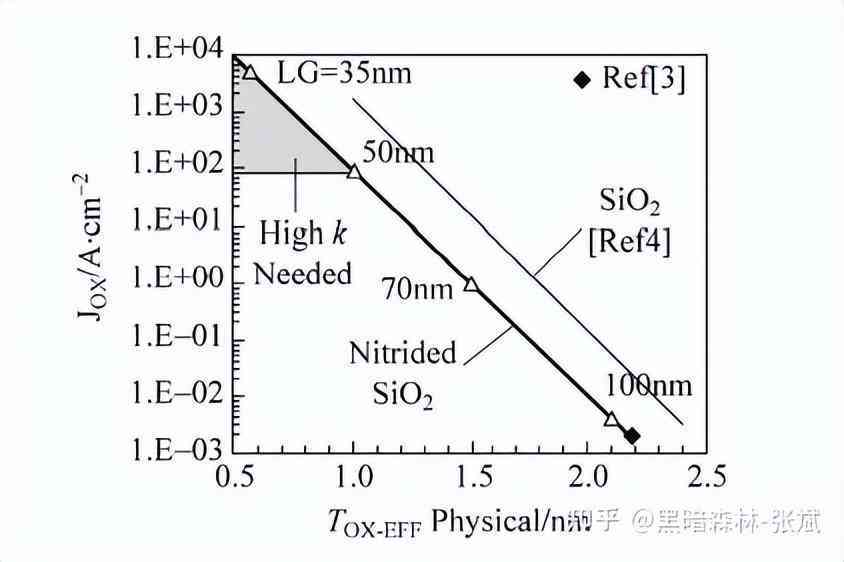

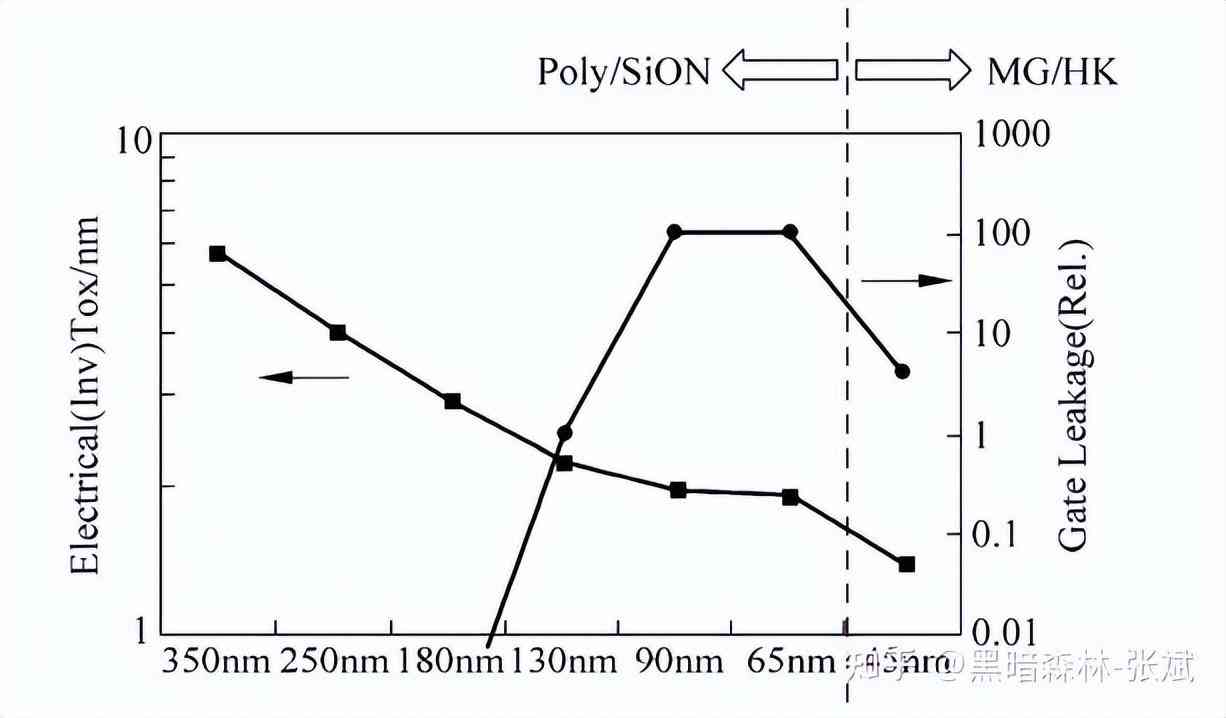

在柵極電介質的沉積方面,為了在降低電介質EOT(等效氧化物厚度)的同時,解決柵極漏電的問題,必須提高材料的k值。在130/90/65nm乃至45nm的世代,對傳統熱氧化生成的氧化硅進行氮化,生成氮氧化硅是提高k值的一種有效方法。而且氮氧化硅在提高材料k值和降低柵極漏電的同時,還可以阻擋來自多晶硅柵內硼對器件的不利影響,工藝的整合也相對簡單。到45/32nm以后,即使采用氮氧化硅也無法滿足器件對漏電的要求,高k介質的引入已經成為必然。Intel公司在45nm已經采用了高k的柵極介質(主要是氧化鉿基的材料,k值約為25),器件的漏電大幅降低一個數量級。

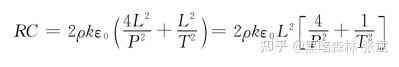

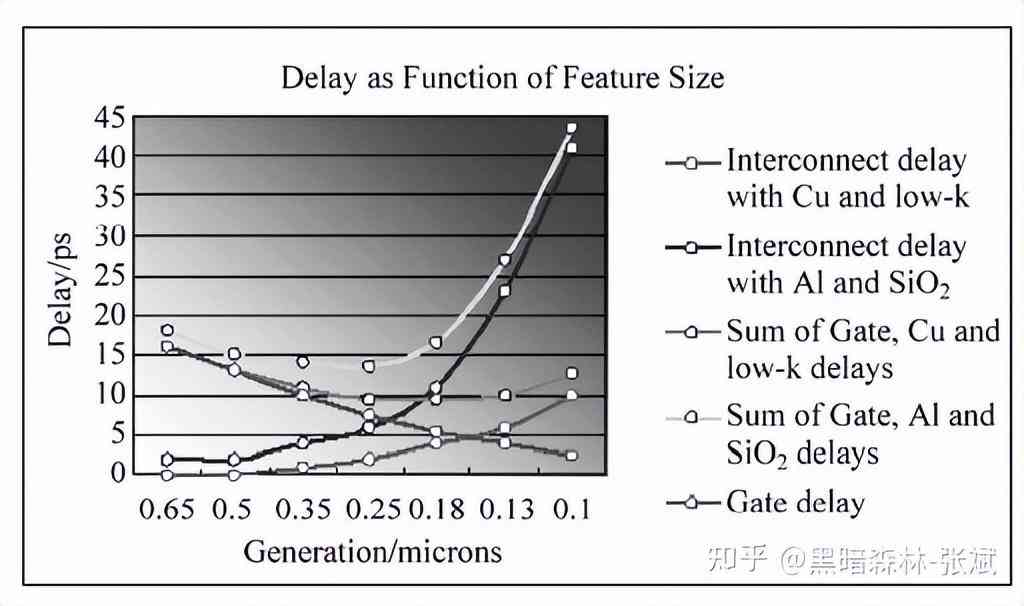

在后端的互連方面,主要的挑戰來自RC延遲。為了降低RC延遲,電介質的k值必須隨著技術節點不斷降低。從180/130nm采用摻氟的氧化硅(FSG)到90/65/45nm采用致密摻碳的氧化硅(SiCOH),再到32nm以后的多孔的摻碳氧化硅(p-SiCOH),材料的k值從3.5到3.0~2.7,再到小于2.5。不僅金屬間電介質,在銅化學機械拋光后的表面沉積的介質阻擋層的k值也必須不斷降低。從130nm采用的氮化硅到90/65/45nm以后采用的摻氮的碳化硅(NDC),材料的k值從7.5到小于5.3。

新的材料可能要求采用新的沉積方法。例如高k的柵極介質,目前主要采用原子層沉積(ALD)的方法,不僅可以更為精確地控制薄膜的厚度,而且沉積溫度低,填充能力好,薄膜內的俘獲電荷少。又如后端的多孔摻碳氧化硅 的沉積 ,在常規的等離子體增強CVD(PECVD)沉積過程中,需要加入造孔劑,然后通過紫外固化的方法除去造孔劑,從而在薄膜內留下納米尺寸的孔隙。

即使采用相同的材料,由于要求的提高也可能需要采用新的沉積方法。在淺槽隔離(STI)和層間電介質(ILD)的沉積,雖然都是沉積氧化硅,但在45nm以后,對填充能力、等離子損傷的要求越來越高,高密度等離子體CVD(HDP-CVD)的方法已經不能滿足要求,基于熱反應的亞常壓CVD(SACVD)已逐漸取代HDP-CVD成為主流。

總而言之,隨著技術節點的推進,對電介質薄膜沉積的材料和工藝都提出了更高的要求,新的材料和工藝將不斷涌現。

氧化硅薄膜和氮化硅薄膜是兩種在CMOS工藝中廣泛使用的介電層薄膜。

氧化硅薄膜可以通過熱氧化(thermal oxidation)、化學氣相沉積 ( chemical vapor deposition ) 和原子 層沉積法 ( Atomic Layer Deposition,ALD)的方法獲得。

如果按照壓力來區分的話,熱氧化一般為常壓氧化工藝,常見的機器有

多片垂直氧化爐管(oxide furnace, TEL或KE),快速熱氧化(Rapid Thermal Oxidation,RTO,應用材料公司)等。

化學氣相沉積法一般有低壓化學氣相沉積氧化(Low Pressure Chemical Vapor Deposition,LPCVD,TEL或KE)工藝,半大氣壓氣相沉積氧化 ( Sub-atmospheric Pressure Chemical Vapor Deposition,SACVD,應用材料公司)工藝,增強等離子體化學氣相層積(Plasma Enhanced Chemical Vapor Deposition,PECVD,應用材 料公司)等,常見的機器有多片垂直氧化沉積爐管(TEL,KE),單片腔體式的沉積機器(應用材料公司)和低壓快速熱退火氧化機器 (應用材料公司)。原子層沉積法獲得的氧化膜也是一種低壓沉積, 在45nm以上的工藝中采用比較少,但在45nm以下工藝技術中開始大量采用,主要是為了滿足工藝的階梯覆蓋率的要求。

在熱氧化工藝中,主要使用的氧源是氣體氧氣、水等,而硅源則是單晶硅襯底或多晶硅、非晶硅等。氧氣會消耗硅(Si),多晶硅(Poly)產生氧化,通常二氧化硅的厚度會消耗0.54倍的硅,而消耗的多晶硅則相對少些。這個特性決定了熱氧化工藝只能應用在側墻工藝形成之前的氧化硅薄膜中。同時熱氧化工藝的氧化速率受晶相(111 >100)、雜質含量、水汽、氯含量等影響,它們都使得氧化速率變快。

具體的方法有:

Si(固態)+O2 (氣態)→ SiO2 (固態)(干氧法)

Si(固態)+ H2O (氣態)→ SiO2 (固態)+2H2 (濕氧法)

化學氣相沉積法使用的氧源有,,O2,O3,N2O 等 , 硅源有TEOS ( tetraethyl or thosilicate , Si(OC2H5)4,SiH4, BTBAS ( 二丁基胺矽烷, Bis( tertiarybutylamino ) ) , TDMAS(Tris(Dimethylamino)Silane)等 。

通過LPCVD多片 垂直爐管得到氧化硅薄膜的方法有:

TEOS(液態)→ SiO2 (固態)+副產物(氣態)(550~ 800℃)

SiH4 (氣態)+ N2O (氣態)→ SiO2 (固態)+副產物(氣態)(650~900℃)

BTBAS+ O2/O3 →SiO2 (固態)+副產物(氣態)(450~ 600℃)

通過單片單腔體的沉積機器獲得氧化硅薄膜的方法有

TEOS+O3 、 SiH4+O2 等,

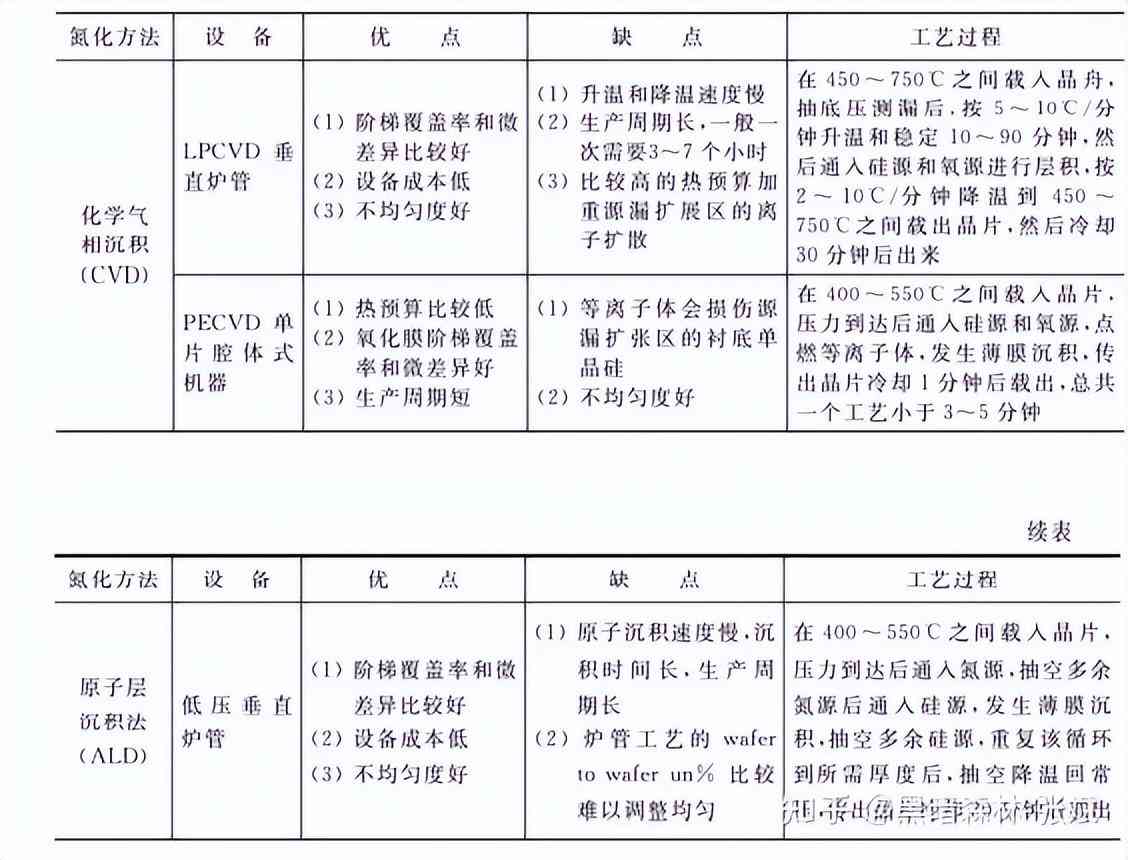

一般的溫度范圍為400~550℃。 具體兩種氧化工藝和制造設備的比較如表4.1所示。

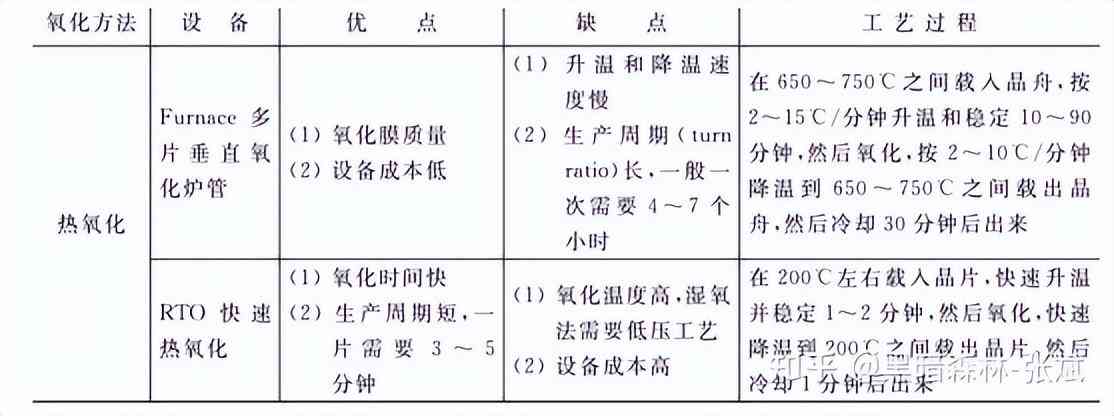

表4.1 熱氧化和化學氣相沉積的工藝和制造設備比較

表4.1 熱氧化和化學氣相沉積的工藝和制造設備比較(續表)

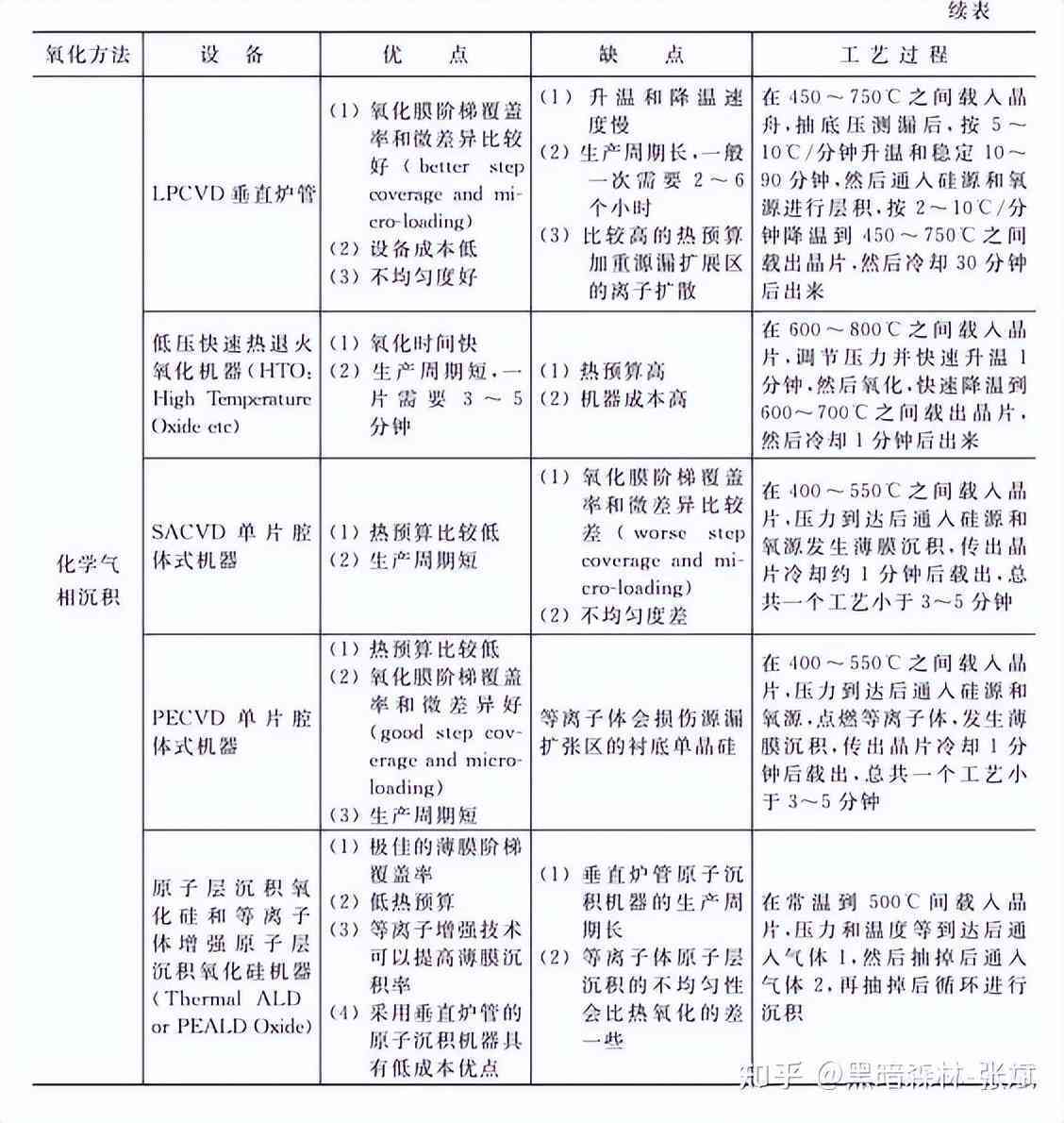

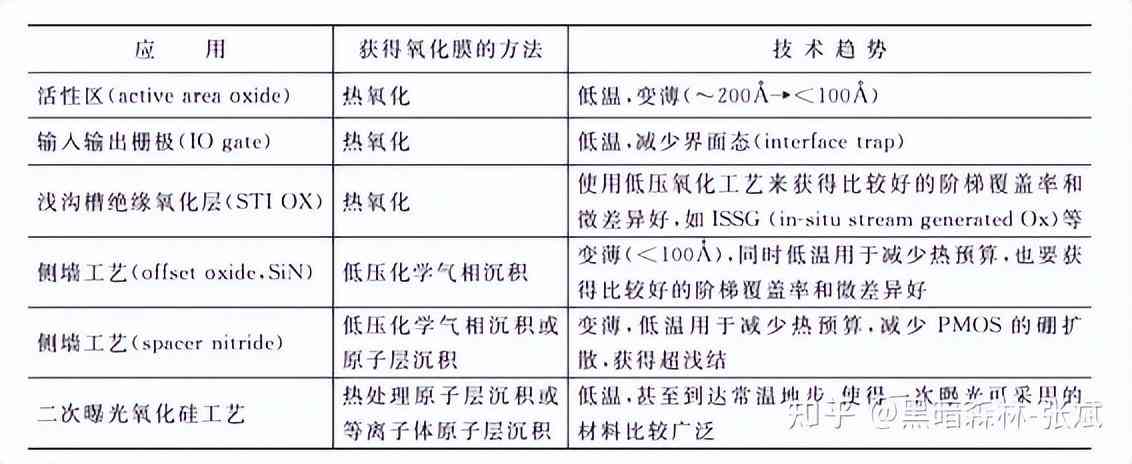

在ULSI的CMOS工藝中,根據氧化膜獲得的方法把它應用在不同地方,如表4.2所示。

表4.2 氧化膜的主要應用

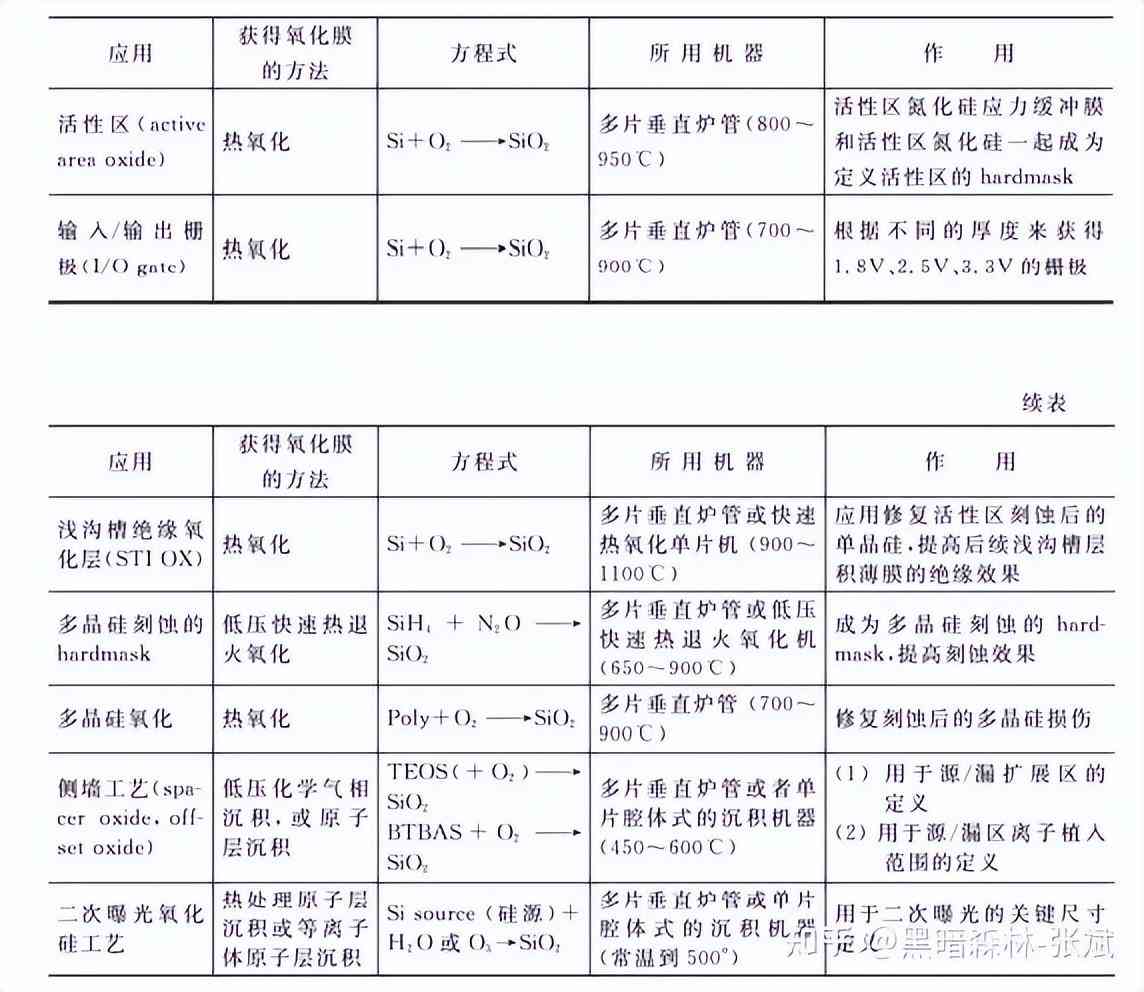

氮化硅薄膜可以通過化學氣相沉積和原子層沉積法的方法獲得,化學氣相沉積法一般有

低壓化學氣相沉積氧化工藝增強等離子體化 學氣相層積等常見的機器有

多片垂直氮化沉積爐管(TEL或KE)單片腔體式的沉積機器(應用材料公司)原子層沉積機器(KE)但原子層沉積法獲得的氮化膜使用比較少。 化學氣相沉積法使用的氮源一般為

NH3硅源有SiH4SiH2Cl2 ( dichlorosilane , DCS )Si2Cl6 ( hexachlorodisilane , HCD )BTBAS ( 二丁基胺硅烷 , Bis ( tertiarybutylamino ) silicate )TDMAS(tris(dimethylamino)silane)通過LPCVD多片垂直 爐管或單片機器得到氮化硅薄膜的方法有

兩種獲得氮化膜的方法的主要優缺點如表4.3所示。

表4.3 化學氣相沉積法和原子層沉積法的主要優缺點

在ULSI的CMOS工藝中,氮化膜的主要應用如表4.4所示。

表4.4 氮化膜的主要應用

氧化硅和氮化硅在90nm以下技術中的主要趨勢如表4.5所示。

表4.5 氧化硅和氮化硅在90nm以下技術中的主要趨勢

在65nm以下,側墻工藝中的氧化硅和氮化硅的熱預算非常重要, 可以通過降低爐管的層積溫度(<600℃),也可以使用單片機的 SACVD OX,PECVD SiN。但過低的溫度會使階梯覆蓋率和微差異變差,同時產生酸槽刻蝕率偏快的問題,需要通過結深工藝和側墻工藝的整合來取舍。

作為柵極氧化介電層從純二氧化硅到HfO,ZrO2 等系列高介電常數薄膜的過渡材料,氮氧化硅為CMOS技術從0.18μm演進到45nm世代發揮了重要作用。時至今日,其技術不管是從設備、工藝、整合還是表征,都越來越成熟,越來越完善。之所以用氮氧化硅來作為柵極氧化介電層,一方面是因為跟二氧化硅比,氮氧化硅具有較高的介電常數,在相同的等效二氧化硅厚度下,其柵極漏電流會大大降低(見圖 4.1);

另一方面,氮氧化硅中的氮對PMOS多晶硅中硼元素有較好 的阻擋作用,它可以防止離子注入和隨后的熱處理過程中,硼元素穿過柵極氧化層到溝道,引起溝道摻雜濃度的變化,從而影響閾值電壓的控制。作為柵極氧化介電層的氮氧化硅必須要有比較好的薄膜特性及工藝可控性,所以一般的工藝是先形成一層致密的、很薄的、高質 量的二氧化硅層,然后通過對二氧化硅的氮化來實現的。也有少量文獻報道用含氮的氣體,如一氧化氮(NO)和氧氣共同反應氧化單晶硅底材來形成氮氧化硅柵極氧化介電層。本節就對氮氧化硅柵極氧化介 電層的制造工藝,表征方法及未來發展方向和挑戰作一簡單介紹。

圖4.1 SiO2 ,SiON,高k 介電材料漏電流和等效厚度的關系

1.氮氧化硅柵極氧化介電層的制造工藝

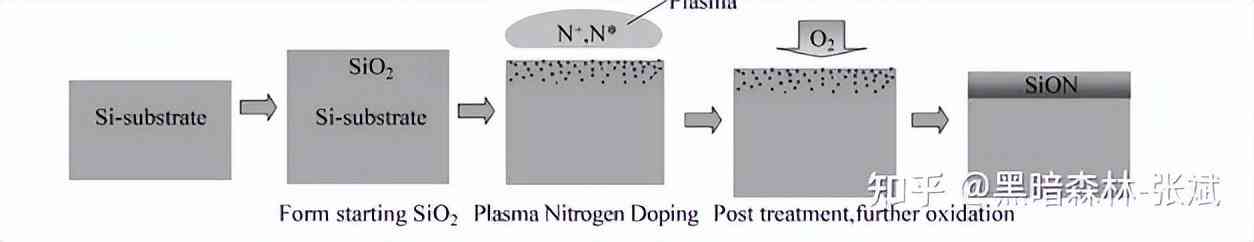

氮氧化硅柵極氧化介電層主要是通過對預先形成的 SiO2 薄膜進行氮摻雜或氮化處理得到的,氮化的工藝主要有熱處理氮化(thermal nitridation)和化學或物理沉積(chemical or physical deposition)兩種。

早期的氮氧化硅柵極氧化層的制備是用爐管或單一晶片的熱處理 反應室來形成氧化膜,然后再對形成的二氧化硅進行原位或非原位的熱處理氮化,氮化的氣體為 N2O 、NO或NH3 中的一種或幾種 。這種氮化方法工藝簡單,可缺點是摻雜的氮含量太少,對硼元素的阻擋作用有限;并且摻雜的氮位置靠近SiO2 和硅底材之間,界面態不如純 氧化硅,對載流子的遷移率、對器件的可靠性都有一定的影響。用熱處理氮化得到的氮氧化硅主要用于0.13μm及以上的CMOS器件中柵極氧化介電層的制備。 用化學或物理沉積(chemical or physical deposition)方式來形成 SiON的方法很多,比如低能量的離子注入、噴射式蒸汽沉積、原子層沉積、等離子體氮化等,隨著CMOS進入90nm以下,柵極氧化介電層及多晶硅的厚度越來越薄,而源漏極及輕摻雜源漏極的摻雜濃度相對越來越高,這就要求作為柵極氧化層的氮氧化硅中,氮的含量越來越高,同時盡可能的靠近上表面。

在這種情況下,等離子體氮化工藝就應運而生。它主要是用氮氣或氮氣和惰性氣體(如氦氣或氬氣)的混合氣,在磁場和電場感應下產生等離子體,而形成的氮離子和含氮的活性分子/原子則通過表面勢擴散至預先形成的超薄氧化硅表面,取代部分斷裂的硅氧鍵中氧的位置,并在后續的熱退火步驟中將已經形成較為穩定的硅氮成鍵而固定來。

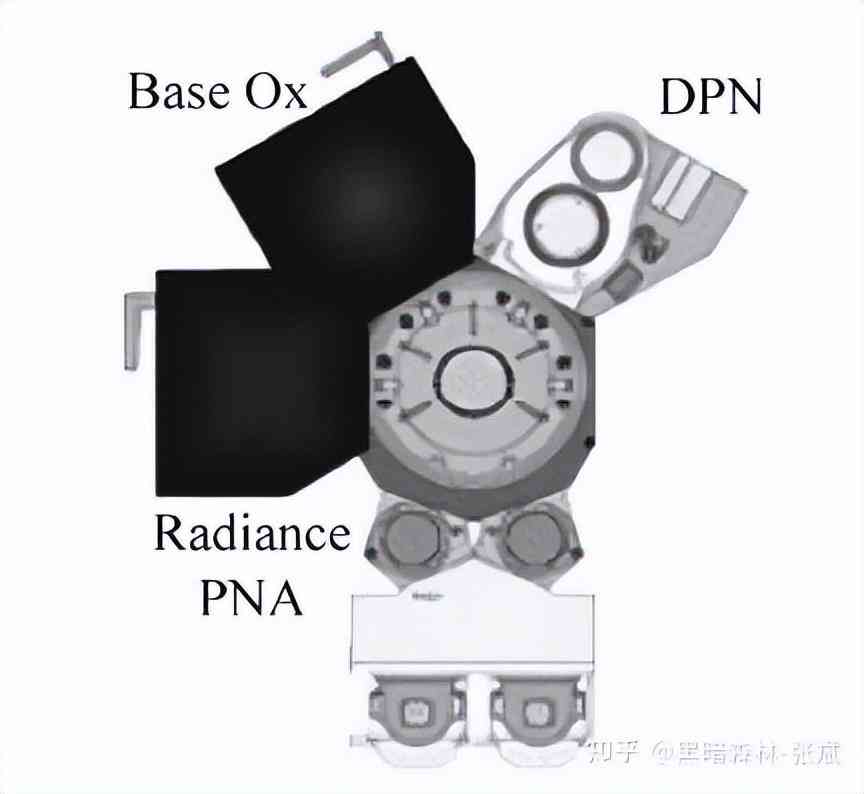

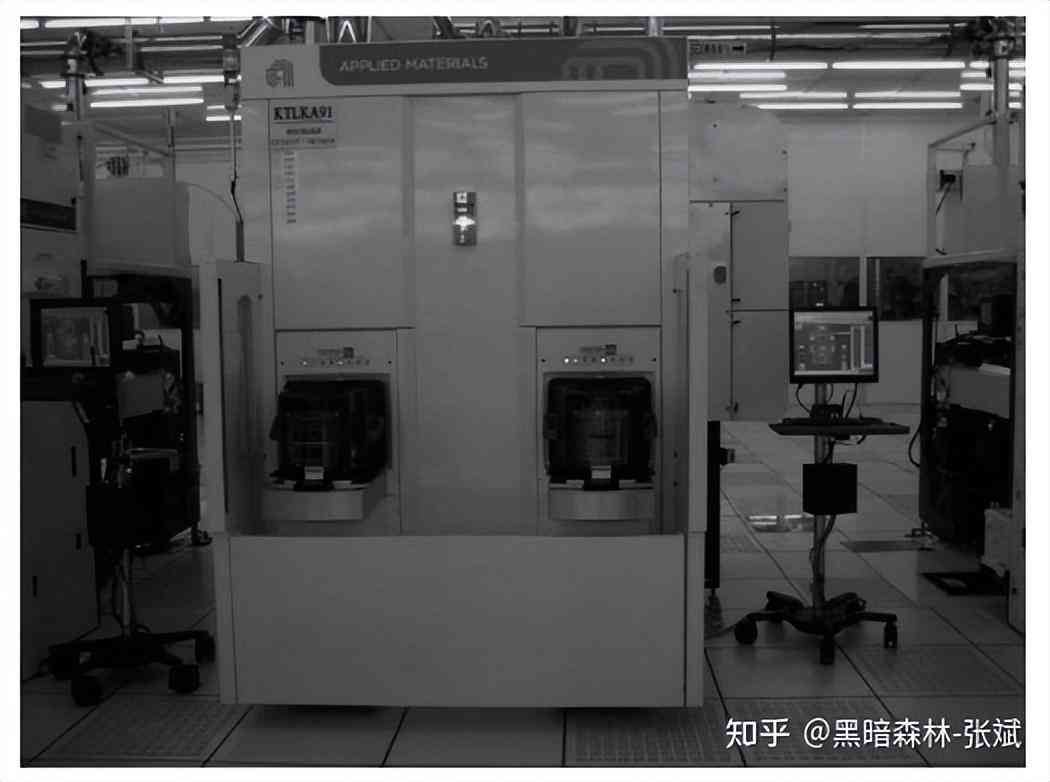

一個典型的等離子體氮氧化硅工藝示意圖如圖4.2所示,它具有工藝可控性和重現性好、形成的氮氧化硅氮含量高、均勻性好等優點。等離子體氮化工藝的主要設備生產商有應用材料公司(Applied Material)和東電電子(Tokyo Electron)。需要特別指出的是,氮氧化硅工藝復雜,材料受外部環境影響較大,不僅前后工藝流程間要控制時間(如與前面的預清洗工藝間,與后面的多晶硅沉積工藝間),本身工藝步驟間也要控制時間間隔和環境條件,所以通常的等離子體氮化工藝設備會把形成SiO2 的腔體。等離子體氮化的腔體及隨后的退火處理腔體都整合在一起(見圖 4.3)

圖4.2 等離子體氮化形成SiON工藝示意圖

圖4.3 應用材料公司用于制造SiON的gate cluster機臺

2.氮氧化硅柵極氧化介電層的表征

跟超薄 SiO2 一樣,當SiON氧化介電層越來越薄時,氮氧化硅膜厚、組成成分、界面態等對器件電學性能的影響越來越重要,同時這些薄膜特性的表征也越來越困難,往往需要幾種技術結合起來使用。

比如說傳統的偏振光橢圓率測量儀除了要求量測的光斑大小越來越小,并具有減少外部環境玷污效應(airborne material contamination effect)的功能外,同時還需具備短波長的紫外光或遠紫外光波段,以提高對氮氧化硅中化學組分的敏感度。

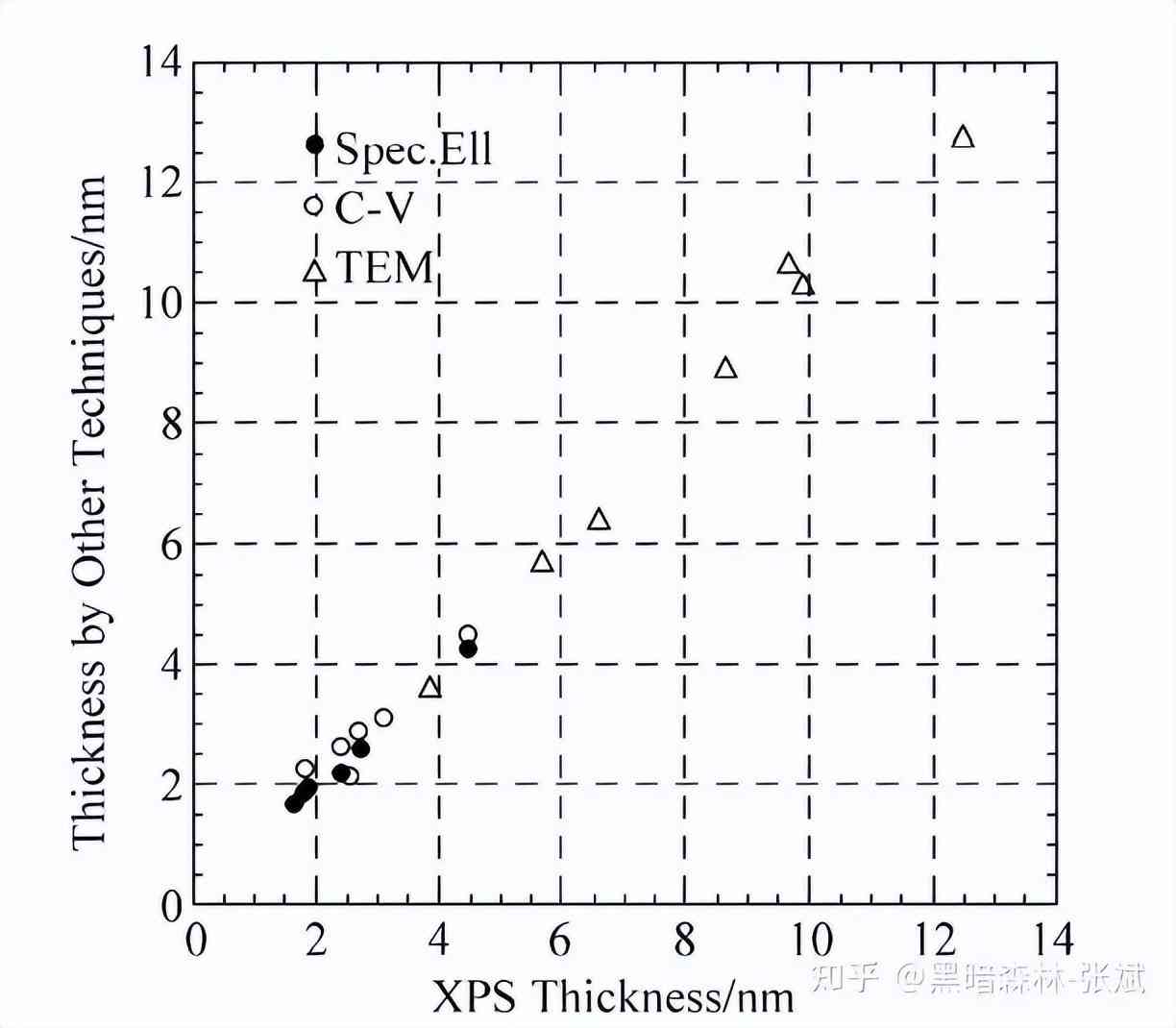

而對透射電鏡來說,高分辨率 (<0.2nm)的透射電鏡對于觀察 SiO2/Si 或SiON/Si的界面形貌、界面缺陷是不可或缺的。而對于氮氧化硅介電層來說,光電子能譜 (XPS)是一種比較有效的測量膜厚和組成成分的工具,它跟TEM和 C-V量測都有比較好的線性關系(見圖4.4),XPS不但可用于SiO2 或SiON柵極氧化介電層的厚度量測,具有角度分辨率的XPS還可以用于SiON中氮的濃度隨深度的分布測試 。

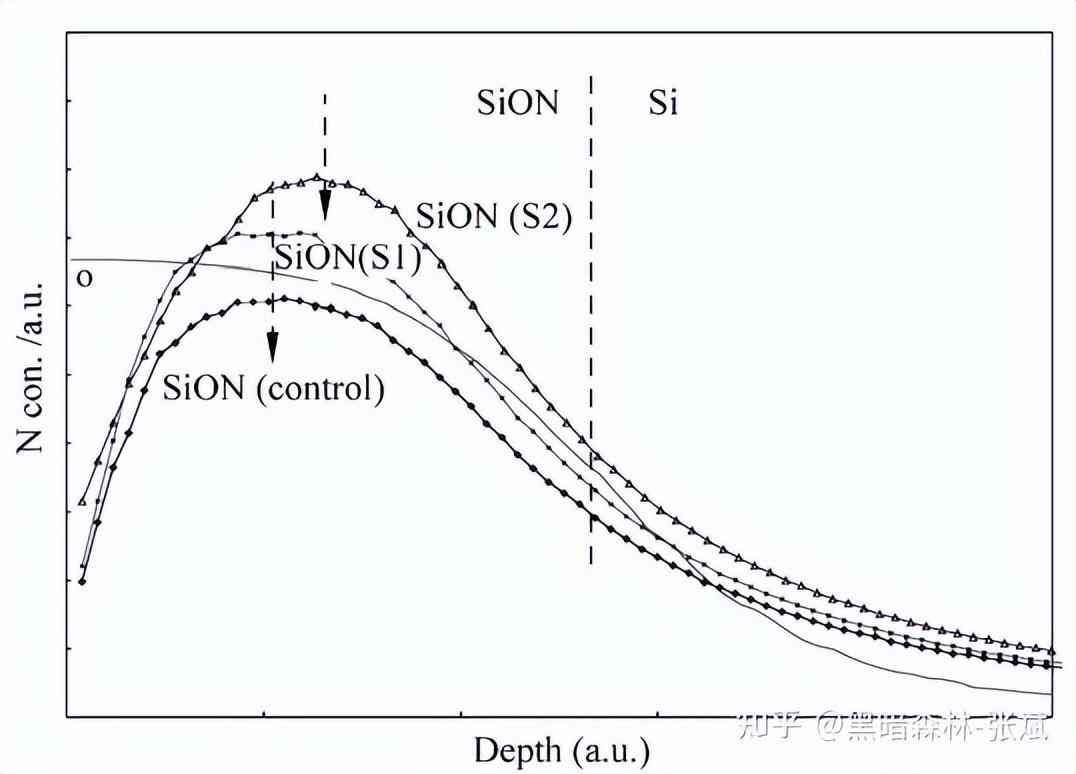

另一種比較有效測量氮氧化硅中氮的濃度分布的工具為二次離子質譜(SIMS),它可以區分不同工藝條件下制得的氮氧化硅介電層厚度、氮的濃度及分布的細微差別(見圖4.5)。對于SiON介電層來說,除了上述特性外,薄 膜界面態、缺陷及電荷情況對介電層的電學性能的影響也至關重要。

這些通常可用非接觸式的C-V測量儀來實現的。非接觸式C-V測量設備不但可以測得超薄SiON介電層的界面電荷,缺陷密度,還可以表征介電層的漏電流特性。以上這些測量基本上是在光片上進行的,對于一個柵極氧化介電層來說,最直接也是最重要的是當它真正用于 CMOS器件時,器件的電學性能、可靠性等,這些則需要用常規的C-V、I-V、GOI、NBTI、HCI等測量來表征

圖4.4 用XPS測得的SiO2 厚度與TEM,C-V測得的厚度的對應關系

圖4.5 用SIMS來分析不同工藝條件SiON介電層的氮濃度及深度分布

3.氮氧化硅柵極氧化介電層的未來發展方向和挑戰

跟二氧化硅比,氮摻雜的SiON柵極氧化層或氧化硅氮化硅疊加的柵極氧化層,其漏電流得到了大大的改善(可降低一個數量級以上),并且可以同時保持溝道里的載流子遷移率不變。

時至今日, SiON柵極介電層還是45nm以上CMOS技術主流的柵極材料。在可預見的將來,氮氧化硅柵極氧化介電層會在現有技術基礎上,不斷提高工藝制程的控制水平,比如用較溫和的等離子體來實現氮摻雜,以減少氮穿透SiO2 到達硅襯底并降低SiON/Si界面的損傷;又比如通過設備 硬件的改進來提高摻氮濃度和介電層厚度的均一性。

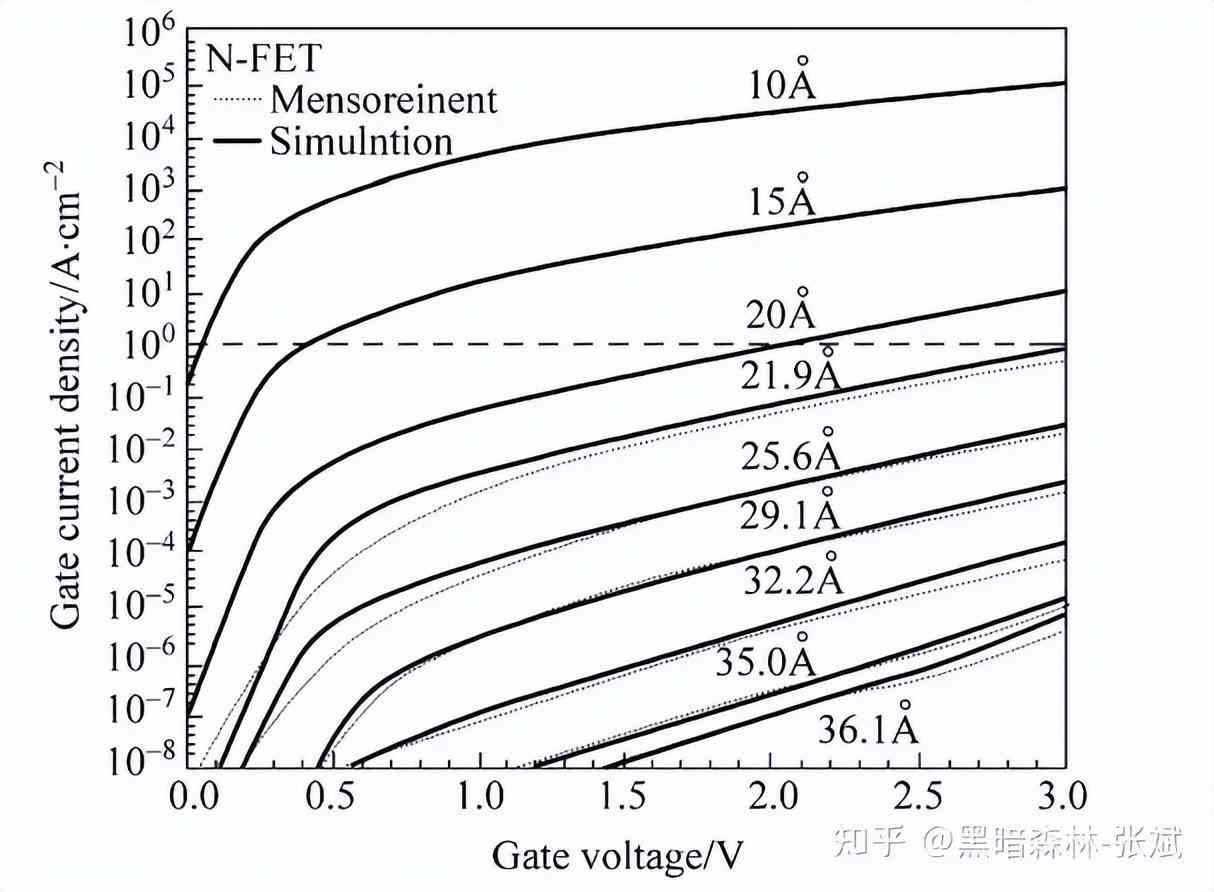

跟高介電常數柵 極氧化層和金屬電極比,SiON制程具有工藝簡單成熟,生產成本低, 重現性好等技術優點。工程技術人員一方面在努力嘗試將它繼續延伸到下一代CMOS技術節點,如32nm和28nm,另一方面也在不斷地拓寬它的應用,如作為32nm及以下技術節點高介電材料和硅底材的中間層。當然,每種技術工藝都有它的局限性,當純粹的SiON柵極 介電層物理厚度降低到小于12~14?時,從柵極到硅襯底的直接隧穿漏電流已經大到直接影響器件的動態、靜態功耗,并決定了器件的可靠性,高介電材料取代氮氧化硅成為新的柵極氧化介電層也已經成為 歷史的必然。

1.介紹

2007年1月27日,Intel公司宣布在45nm技術節點采用高k介質和金屬柵極并進入量產,這是自20世紀60年代末引入多晶硅柵極后晶體管技術的最大變化。很快地,IBM公司于2007年1月30日也宣布用于生產的高k介質和金屬柵極技術。在32nm和28nm技術節點,已經有越來越多的公司采用這一技術。

為什么要采用高k 柵極介質呢?

器件尺寸按摩爾定律的要求不斷縮小,柵極介質的厚度不斷減 薄,但柵極的漏電流也隨之增大。在5.0nm以下, SiO2 作為柵極介質所產生的漏電流已無法接受,這是由電子的直接隧穿效應造成的。對SiO2進行氮化,生成SiON可以使這一問題得以改善,但是在90nm節點后,如圖4.6所示,由于柵極漏電流過大,即使采用SiON也難以繼續減薄了(11~12?)。

圖4.6 不同SiON厚度的柵極電壓和漏電流

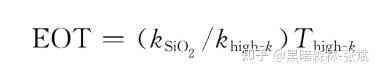

在65nm節點,柵極介質厚度的減薄實際已經停止(見圖4.7),技術的重點在于通過應變硅技術提高器件的性能。但是工業界早在20世 紀90年代末就已認識到,要從根本上解決柵極的漏電問題,必須采用 一種高k介質取代 SiO2/SiON ,這樣可以在降低等效二氧化硅絕緣厚度 (EOT)的同時,得到較大的柵極介質的物理厚度,從而在源頭上堵 住柵極的漏電。介質的EOT公式如下

圖4.7 Intel公司不同技術接點的EOT和柵極漏電流

在維持T high- k 不變的前提下,由于高k 介質的介質常數比SiO2/SiON 的大,EOT就越小,晶體管的尺寸就能按照摩爾定律的要求繼續得以 縮小。如圖4.7所示,Intel公司在45nm采用高k 介質后,EOT降低的同 時,柵極的漏電也呈數量級的減小。

2.高k介質的選擇

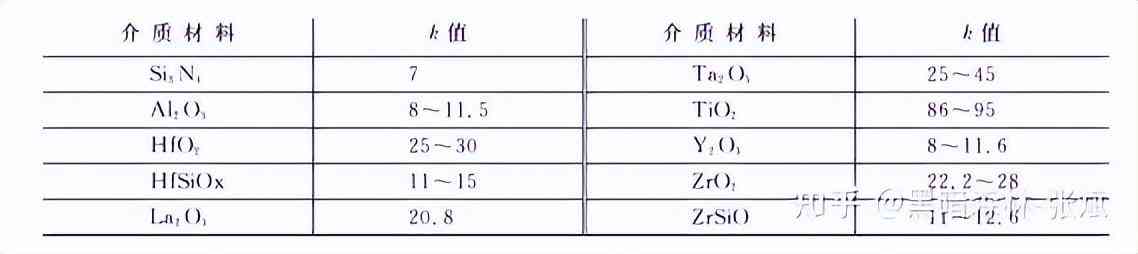

如何選擇高k介質呢?首先高的k 值是一個主要的指標。表4.6列出了候選的介質和它們的k值。根據材料的化學成分、制備方法和晶體結構等條件的不同,同一種材料可能具有不同的k值。

表4.6 介質和它們的k值

除了高的k值,介質同時還必須考慮材料的勢壘、能隙、界面態密度和缺陷、材料的化學和熱穩定性、與標準CMOS工藝的兼容性等因素。

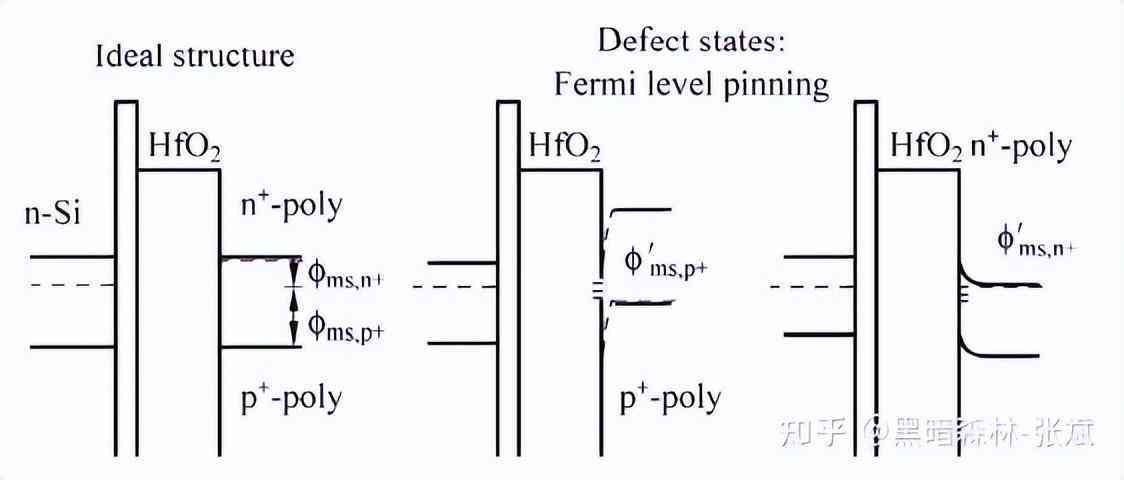

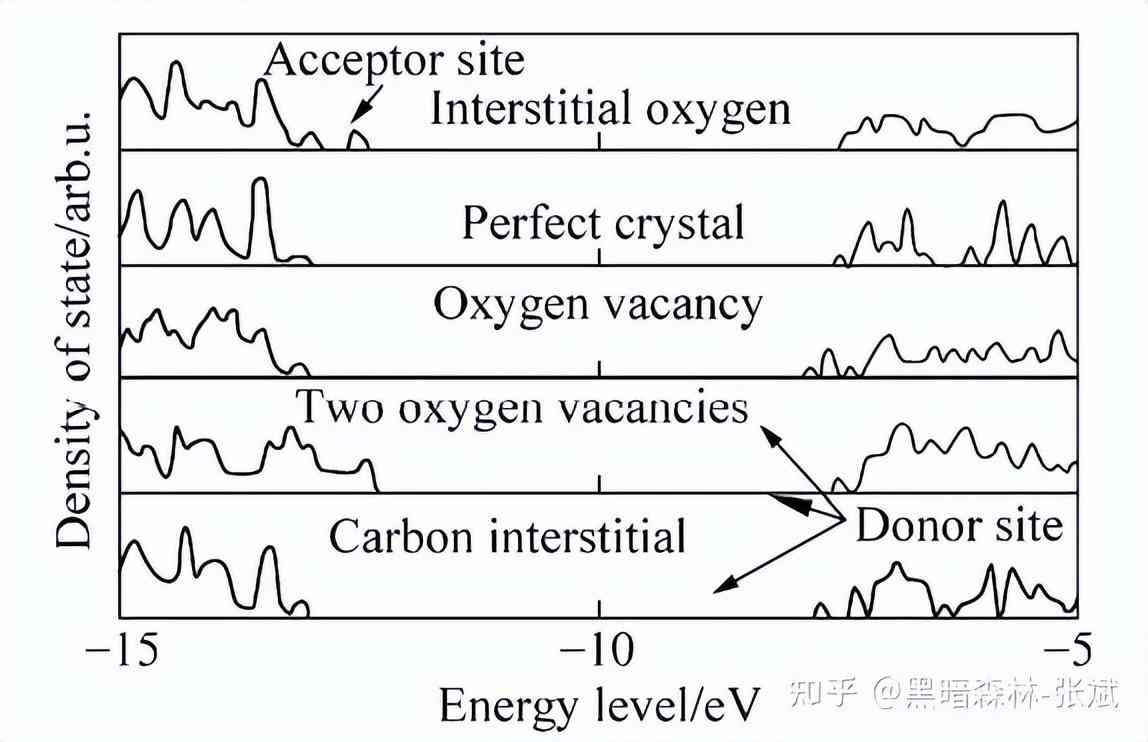

HfO2 族的高k 介質是目前最有前途的選擇之一(其次是ZrO2 族的高k介質)。 在高k介質研究的前期,介質與多晶硅柵極的兼容性一直是一個問題。如圖4.8所示,由于在HfO2 和多晶硅界面上形成Hf-Si鍵合,即界面存在缺陷態,使得無法通過多晶硅的摻雜調節器件的開啟電壓 ( Vt ),這被稱為“費米能級的釘扎”。

圖4.8 費米能級的釘扎

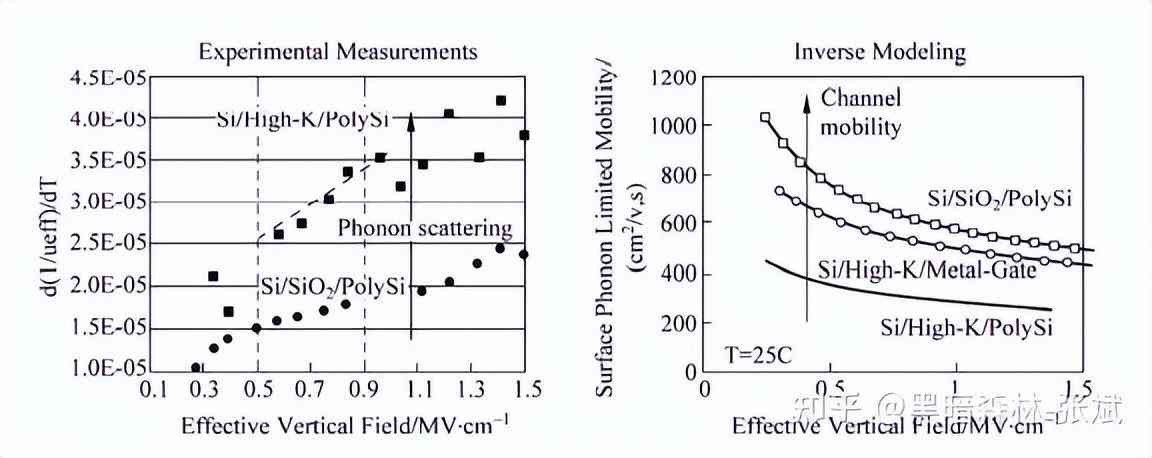

另外一個問題是器件的電遷移率的降低,這是由于高k介質的表面聲子散射造成的(見圖4.9)。因為高k介質的高的k值得益于其偶極性分子結構,但這種分子結構容易產生振動。在和硅的界面上,偶極性分子的振動被傳遞到硅原子,造成晶格振動(聲子)并進而影響電子的正常運動,導致遷移率的降低。

圖4.9 不同結構下的電子遷移率

問題的解決方法之一是采用金屬代替多晶硅作為柵極,這樣既可 以避免HfO2 和多晶硅界面上缺陷態的產生,同時金屬柵極的高的電子 密度,可以把偶極性分子的振動屏蔽掉,從而提高器件的通道內的遷 移率(見圖4.9)。 如前所述,HfO2 族的高k介質是目前最好的替代 SiO2/SiON 的選擇。根據工藝整合的不同,主要有先柵極和后柵極兩種路線,在后柵極中又有先高k和后高k兩種不同方法(在金屬柵極章節內詳述),其主要區別在于高k介質是否經歷源/漏的高溫熱處理(1050℃)。純的HfO2 具有較高的k值(25),但缺點是無法承受高溫。在溫度超過 500℃, HfO2 會發生晶化,產生晶界缺陷,同時晶化還會造成表面粗糙度的增加,這都會引起漏電流的增加,從而影響器件的性能。所以純的HfO2 只適合應用于后柵極后高k的整合路線。可以通過對HfO2 進行摻雜來改善它的高溫性能,如摻Si或氮化,形成HfSiO/HfSiON。但 這樣都會降低介質的k值(15),從而影響EOT的降低。

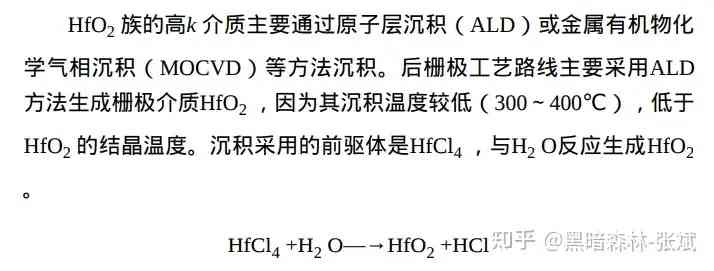

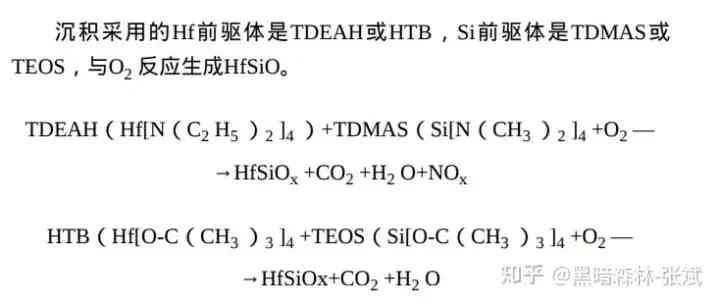

3.高k介質的沉積方法

前柵極工藝路線主要采用MOCVD沉積HfSiO,然后通過熱或等離 子氮化生成HfSiON。沉積溫度較高(600~700℃),因為較高的沉積 溫度配合后續高溫的氮化和氮化后熱處理(1000℃),有助于去除薄膜中的C雜質,已知C雜質會在HfO2 中形成施主能級,增大薄膜的漏 電流(見圖4.10)。

圖4.10 雜質C對HfO2 的不利影響

4.界面層

高k介質的一個挑戰是維持器件的高驅動電流,如前所述,在高k介質上面采用金屬電極取代多晶硅,可以減少溝道內電子遷移率損失,但還需要在高k介質和Si基底之間加入 SiO2/SiON 作為界面緩沖層,進一步改善電子遷移率。

界面層還有助于界面的穩定性和器件的可靠性,因為在以前多個技術節點, SiO2/SiON 與Si基底界面的優化已經研究得十分深入了。

當然,界面層的存在也有不利的一面,它使得整體柵極介質(由低k值的 SiO2/SiON 和高k值的HfO2 族介質構成) 的k值降低,從而影響EOT的降低,所以必須嚴格控制它的厚度。界面層的形成可以采用Si的高溫氧化(如ISSG工藝),或化學氧化來實現。

5.覆蓋層

高k介質的另一個挑戰是Vt的調節。多晶硅柵極可以通過不同的摻雜實現(P型和N型),金屬柵極則需要找到適合PMOS和NMOS的具有不同功函數的金屬材料。不幸的是大多數柵極金屬材料在經過源/漏高溫熱處理后,功函數都會漂移到帶隙中間,從而失去Vt調節的功用(詳述見金屬柵極章節)。

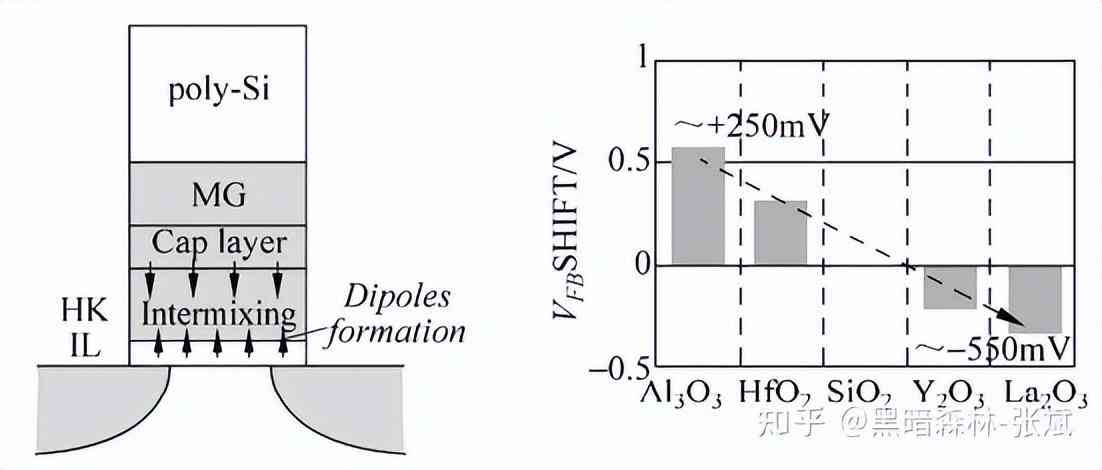

所以對于先柵極工藝,通常采用功函數位于帶隙中間的金屬(如TiN),而通過在高k介質上(或下)沉積不同的覆蓋層來調節Vt 。對NMOS,覆蓋層需要含有更加電正性的原子(La2O3 ),而對PMOS,覆蓋層需要含有更加電負性的原子(Al2O3 )。在高溫熱處理后,覆蓋層會與高k介質/界面層發生互混,在高k介質/界面層的界面上形成偶極子,從而起到Vt調節的作用。圖 4.11表示不同覆蓋層對平帶電壓的影響,可以看到這種方法對NMOS的作用十分明顯(La2O3 ),而對PMOS,效果則不顯著( Al2O3 ),而且由于Al2O3 的k值較低,PMOS的EOT也會受到影響。

圖4.11 覆蓋層對Vt的調節效果

采用覆蓋層對工藝的整合也是一個挑戰,需要在PMOS和NMOS 上分別沉積不同的厚度僅為1nm左右的覆蓋層,去除的同時又不能對高k介質造成損傷,是十分困難的。 覆蓋層的沉積主要有ALD或物理氣相沉積(PVD)技術。PVD通常采用金屬沉積(La和Al)后加氧化來實現。

隨著半導體技術的飛速發展,半導體器件的特征尺寸顯著減小, 相應地也對芯片制造工藝提出了更高的要求,其中一個具有挑戰性的 難題就是絕緣介質在各個薄膜層之間均勻無孔的填充,以提供充分有 效的隔離保護,包括淺槽隔離(shallow-trench-isolation)、金屬前絕緣層(pre-metal-dielectric)、金屬層間絕緣層(inter-metal-dielectric) 等。 高密度等離子體化學氣相沉積(HDP-CVD)工藝自20世紀90年代中期開始被先進的芯片工廠采用以來,以其卓越的填孔能力、穩定的沉積質量、可靠的電學特性等諸多優點而迅速成為0.25μm以下先進工藝的主流。

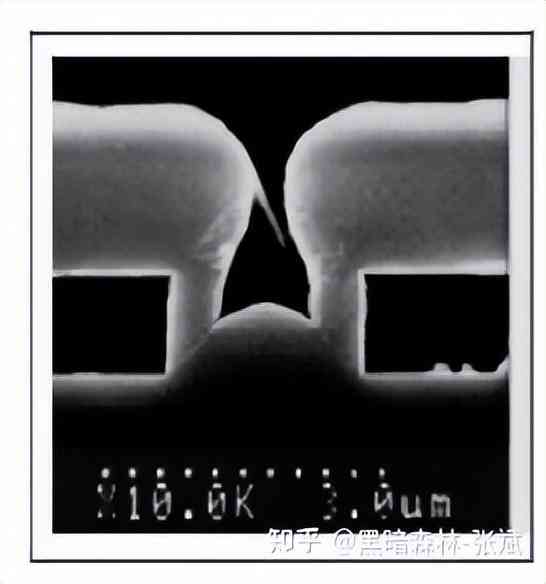

在HDP-CVD工藝問世之前,大多數芯片廠普遍采用等離子體增強化學氣相沉積(PE-CVD)進行絕緣介質的填充。這種工藝對于大于 0.8μm的間隔具有良好的填孔效果,然而對于小于0.8μm的間隔,用 PE-CVD工藝一步填充這么高的深寬比(定義為間隙的深度和寬度的比值)的間隔時會在間隔中部產生夾斷(pinch-off)和空穴(見圖 4.12)。

圖4.12 PE-CVD填充產生pinch-off

其他一些傳統CVD工藝,如常壓CVD(APCVD)和亞常壓 CVD(SACVD)雖然可以提供對小至0.25μm的間隔的無孔填充,但這些缺乏等離子體輔助沉積產生的膜會有低密度和吸潮性等缺點,需要增加PE-CVD薄膜對其進行保護,或者進行后沉積處理(如退火回流等)。

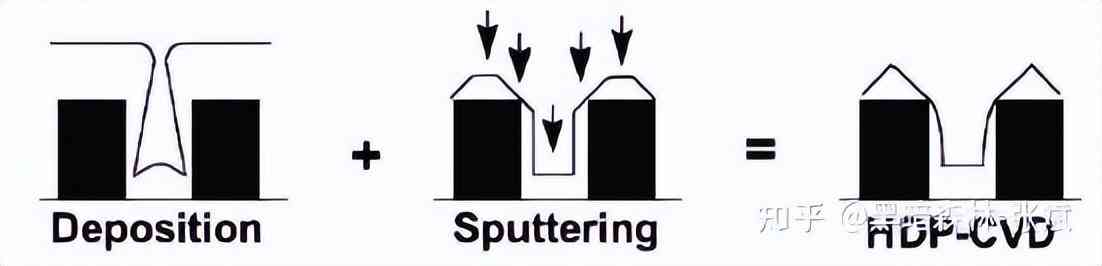

這些工序的加入同樣提高了生產成本,增加了整個工藝流程的步驟和復雜性。 為了同時滿足高深寬比間隙的填充和控制生產成本,誕生了HDP-CVD工藝,它的特點在于,可以在同一個反應腔中同步地進行沉積和物理轟擊(見圖4.13),從而實現絕緣介質在溝槽中的bottom-up生長

圖4.13 HDP-CVD工藝沉積同時進行原位物理轟擊

1.HDP-CVD作用機理

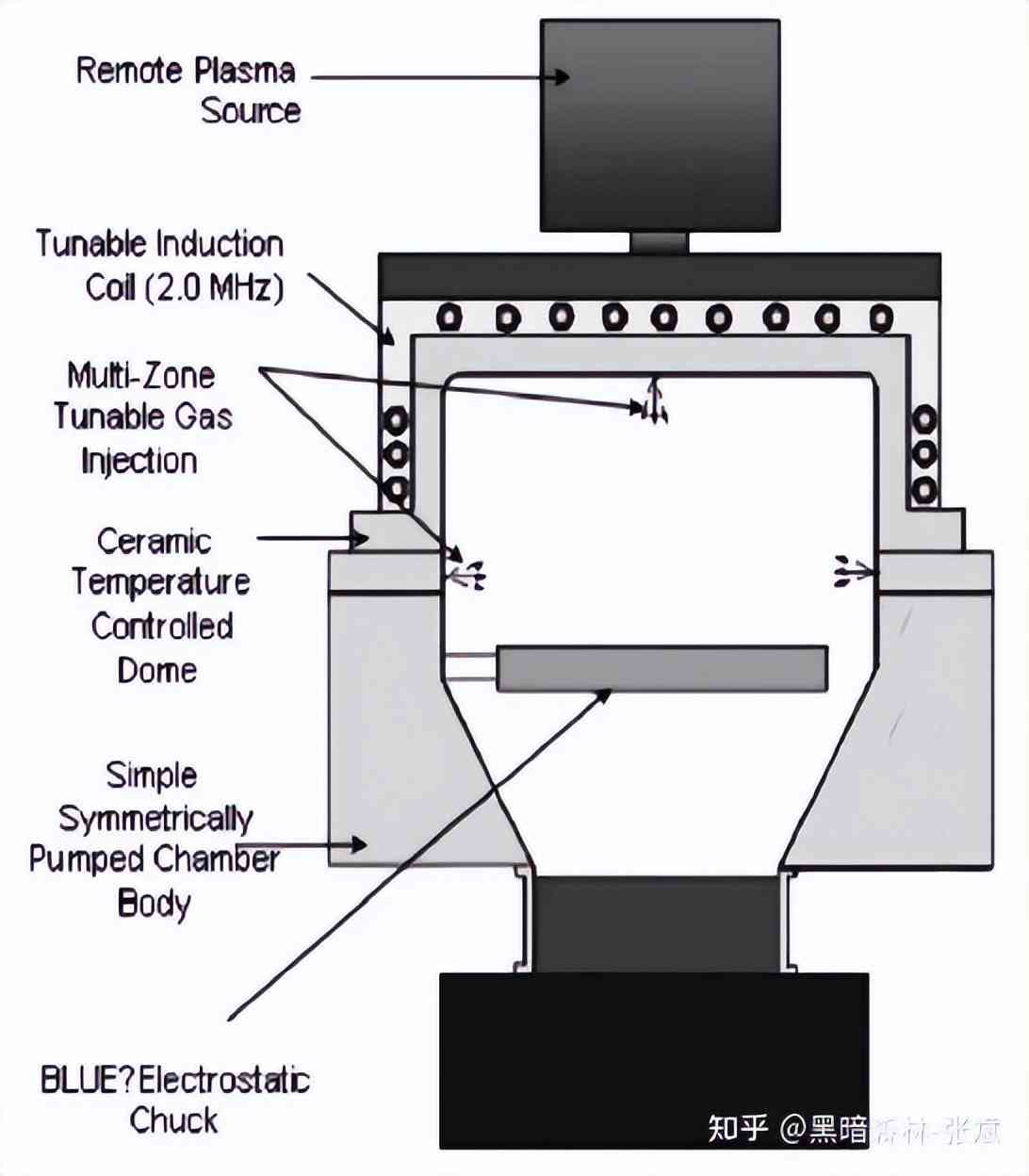

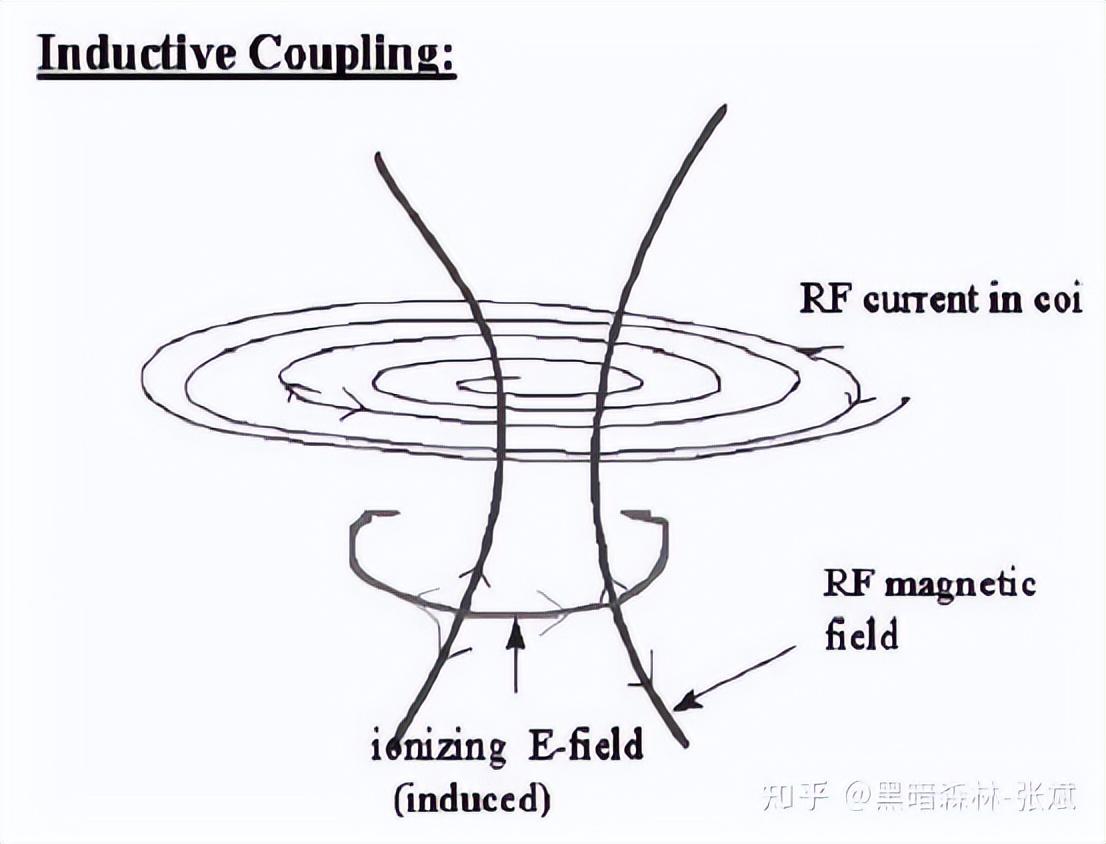

為了形成高密度等離子體,需要有激發混合氣體的射頻(RF) 源,并直接使高密度等離子體到達硅片表面。在HDP-CVD反應腔中 (見圖4.14),主要是由電感耦合等離子體反應器(ICP)來產生并維持高密度的等離子體。當射頻電流通過線圈(coil)時會產生一個交流磁場,這個交流磁場經由感應耦合即產生隨時間變化的電場,如圖4.15所示。

電感耦合型電場能加速電子并能形成離子化碰撞。由于感應電場的方向是回旋型的,因此電子也就往回旋方向加速,使得電子因回旋而能夠運動很長的距離而不會碰到反應腔內壁或電極,這樣就能在低壓狀態(幾個mT)下制造出高密度的等離子體。

圖4.14 應用材料HDP-CVD反應腔

圖4.15 電感耦合等離子體反應器(ICP)工作原理示意圖

為了實現HDP-CVD的bottom up生長,首先要給反應腔中的高能離子定方向,所以沉積過程中在硅片上施加RF偏壓,推動高能離子脫離等離子體而直接接觸到硅片表面,同時偏壓也用來控制離子的轟擊能量,即通過控制物理轟擊控制CVD沉積中溝槽開口的大小。在HDP-CVD 反應腔中 , 等離子體離子密度可達 1011 ~1012 / cm3 ( 2 ~ 10mT)。由于如此高的等離子體密度加上硅片偏壓產生的方向,使 HDP-CVD可以填充深寬比為4:1甚至更高的間隙。

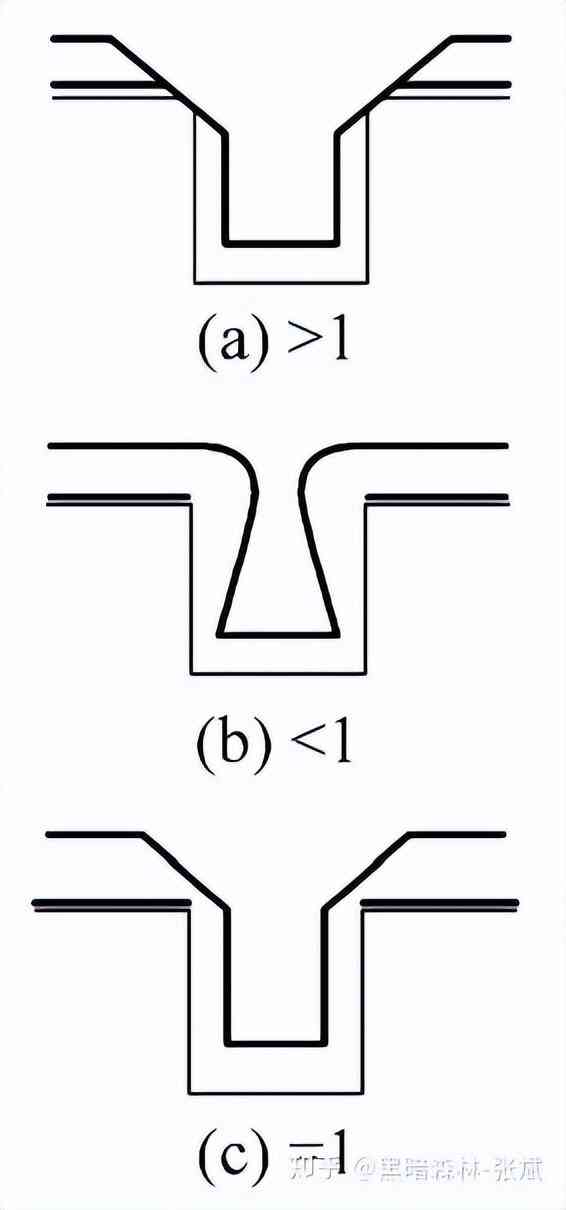

3.HDP-CVD工藝重要參數-沉積刻蝕比

如前所述,HDP-CVD工藝最主要的應用也是其最顯著的優勢就是間隙填充,如何選擇合適的工藝參數來實現可靠無孔的間隙填充就成為至關重要的因素。在半導體業界,普遍采用沉積刻蝕比(DS ratio)作為衡量HDP-CVD工藝填孔能力的指標。沉積刻蝕比的定義是

沉積刻蝕比=總沉積速率/刻蝕速率=(凈沉積速率+刻蝕速率)/刻蝕速率實現對間隙的無孔填充的理想條件是在整個沉積過程中始終保持間隙的頂部開放,以使反應物能進入間隙從底部開始填充,也就是說,我們希望在間隙的拐角處沉積刻蝕比為1,即凈沉積速率為零。對于給定的間隙來說,由于HDP-CVD工藝通常以SiH4 作為絕緣介質中Si 的來源,而SiH4 解離產生的等離子體對硅片表面具有很強的化學吸附性,導致總沉積速率在間隙的各個部位各向異性,在間隙拐角處的總沉積速率總是大于在間隙底部和頂部的總沉積速率;

另外,刻蝕速率隨著濺射離子對于間隙表面入射角的不同而改變,最大的刻蝕速率產生于45~70之間,正好也是處于間隙拐角處,因此需要優化沉積刻蝕比來得到最好的填充效果。圖4.16即是HDP-CVD工藝在不同沉積刻蝕比下對間隙填充情況的示意圖。要得到優化的沉積刻蝕比,最主要的影響因素包括反應氣體流量、射頻(包括電感耦合和偏壓)的功率、 硅片溫度、反應腔壓力等

圖4.16 不同沉積刻蝕比的填充

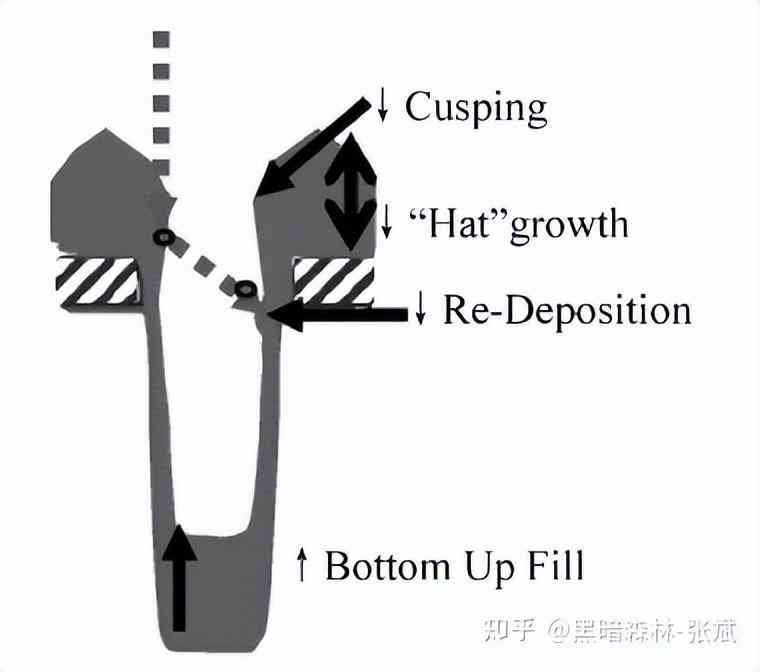

4.HDP-CVD中的再沉積問題

另外,在HDP-CVD中的物理轟擊遵循碰撞中的動量守恒原理,因此被濺射出的物質存在一定角度。隨著溝槽開口尺寸變小,當轟擊離子質量較大時,被轟擊掉的部分會有足夠的能量重新沉積到溝槽側壁另一側某一角度處,使得這些地方薄膜堆積,過多的堆積將會造成溝槽頂部在沒有完全填充前過快封口(見圖4.17)。

隨著器件尺寸減小,填充能力的挑戰越來越大。為了減少物理轟擊造成的再沉積, HDP中的轟擊氣體主要經歷了Ar→O2 →He→H2 的變化,通過降低轟擊原子的質量來改善再沉積引起的填充問題。但是僅僅通過轟擊物質的改變,溝槽填充能力的改善是有限的。

圖4.17 HDP-CVD中的再沉積

所以在90nm以后,為改善物理轟擊所造成的問題,引入同位化學刻蝕對填充結構輪廓進行調整,即在溝槽頂部封口前將其重新打開而不造成再沉積,使得薄膜可以bottom-up填滿整個溝槽。其中NF3 的干法刻蝕被認為是一種非常有效的方法。NF3 在等離子體中離解形成含 氟的活性基團,它可以打斷已沉積薄膜中的Si-O鍵,形成揮發性的SiF4隨著多余的 O2 一起被抽走,從而打開溝槽頂部。但是這種單步沉積-刻蝕-沉積對填充能力的改善是有限的。

通過多步循環沉積-刻蝕-沉積來實現對所填充結構輪廓的調整,來降低溝槽填充的難度。這樣可以在保持HDP本身填充能力的同時,通過 NF3 的刻蝕來重新調整溝槽的形狀,使得更多的材料可以填充進去,保證溝槽不封口形成孔洞。

5.輪廓修正(多步沉積-刻蝕)的HDP-CVD工藝

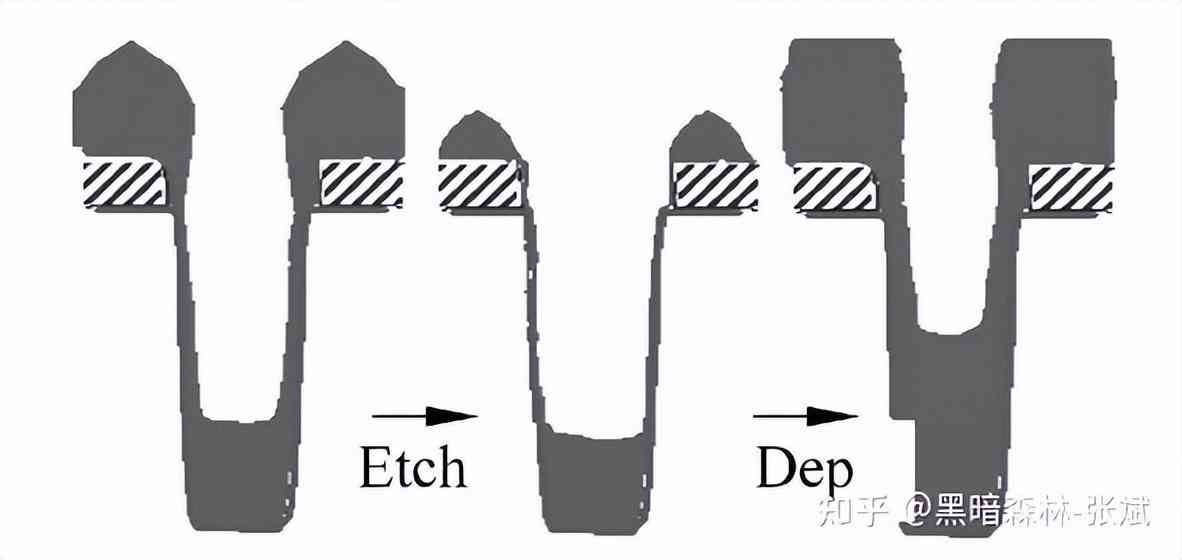

圖4.18是一個典型的多步沉積-刻蝕HDP-CVD的工藝。與一般的 HDP相似,主要通過 SiH4 和O2 反應來形成SiO2 薄膜。但是沉積過程的要求與傳統的HDP不同,傳統的HDP-CVD要求側壁沉積盡可能薄以提供足夠的開口使反應粒子可以到達溝槽底部,最大限度實現從底部到頂部的填充。

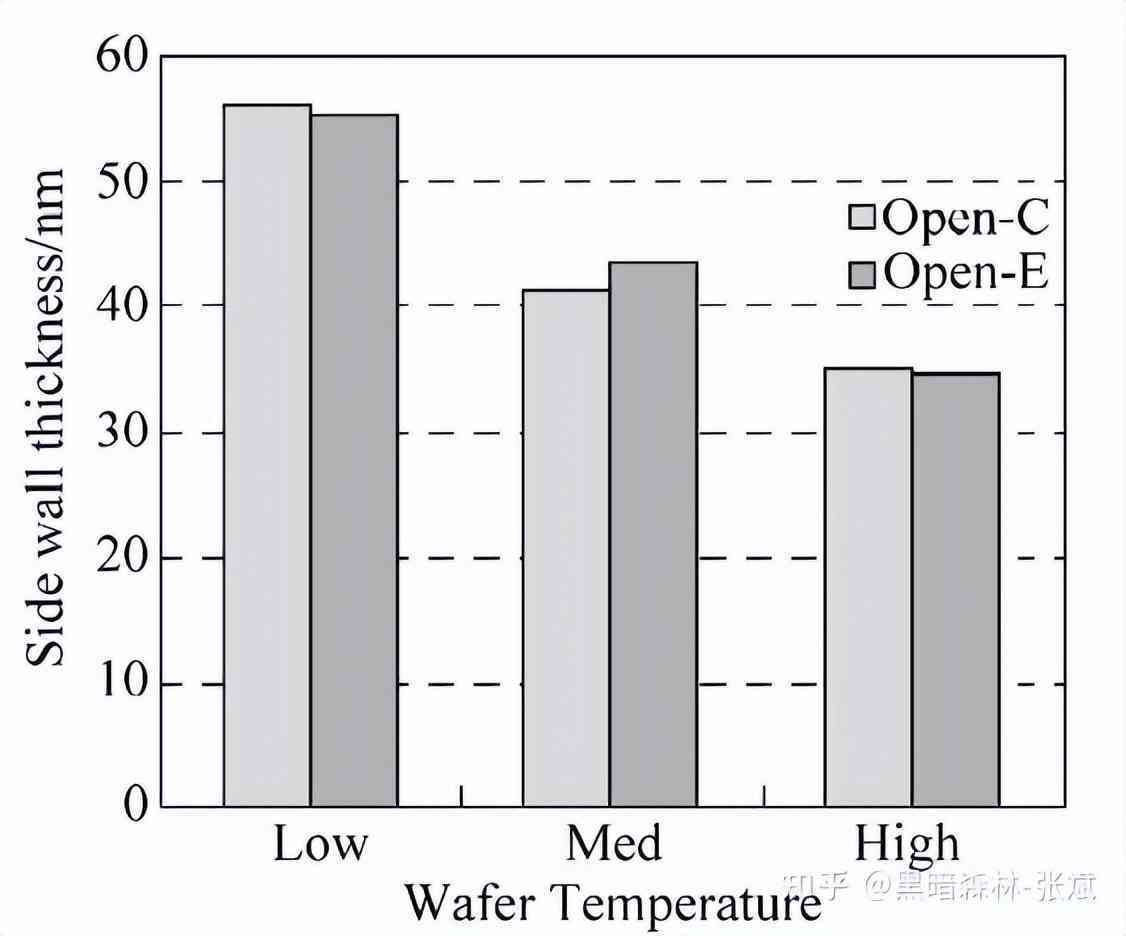

但是多步DEP-ETCH的HDP-CVD主要是以SiO2 的刻蝕為主導的,因此輪廓結構的控制更重要,最優化的沉積應該有足夠厚的側壁保護,對稱的沉積輪廓。應用材料的研究表明(見圖4.19),較低的沉積溫度(230~600℃)能夠很大地改善側壁的保護但又不損傷填充能力,同時可以通過調節沉積溫度將薄膜的應力從180MPa調到 100MPa。一旦沉積條件確定后,填充能力可以通過每個循環中沉積和 刻蝕的量來優化。降低每個沉積過程的沉積厚度可以實現更多次的輪廓調整,但是這樣會增加沉積時間也引入更多的F,有可能會對器件可靠性造成影響。而沉積過程中的物理轟擊氣體分子量越大,可以在溝槽頂部形成Cusping來以保護溝槽頂部在刻蝕過程中不被損傷。目前主要采用He為主的He/H2 混合,主要想通過保證填充能力的同時為溝槽頂部提供足夠的保護。

圖4.18 多步沉積-刻蝕HDP-CVD的工藝

圖4.19 側壁厚度與沉積溫度關系

刻蝕過程是多步dep-etch的關鍵步驟,刻蝕過程通過與NF3 的反應去除掉SiO2 ,由于 NF3 在溝槽不同部位的入射角不同,可以實現頂部刻蝕較多從而可以修整部分填充后的溝槽的形狀得到更容易填充的溝槽結構。刻蝕過程所采用的載氣為H2 ,載氣的分子量越小,可以盡量減少物理轟擊的效果。

另外刻蝕的對稱性對最后的完全填充非常重要,尤其在晶片邊緣,由于Fradical的方向性,這種不對稱性就更加嚴 重,可以通過調節壓力、NF3 氣體流量、襯底偏壓大小以及刻蝕化學物質來對對稱性進行優化。刻蝕的量必須進行非常好的控制。對于特定的溝槽結構,要進行沉積和刻蝕量的優化,盡可能達到填充、沉積速率以及刻蝕Window的平衡。

另外為了盡可能降低薄膜中由于NF3 刻蝕而引入的F。刻蝕結束后,引入Ar/O2/He/H2 等離子體處理可以去除薄膜中所殘留的F,通過調整等離子體處理的時間和功率大小可以優化等離子體處理工藝,將薄膜中的F含量降低到0.07at.%。

多步沉積-刻蝕填滿溝槽后,進一步沉積一層高溫的SiO2 薄膜,作用有二,進一步去除薄膜中殘留的F以及提高薄膜的質量。

1.為什么SACVD被再次使用

對于技術節點為亞65nm、器件深寬比大于8的結構來說,人們發現用這種多步的沉積-刻蝕雖然能夠改善HDP的填充能力,但是會使工藝變得非常復雜,沉積速度變慢,而且隨著循環次數的增加,刻蝕對襯底的損傷會變得更加嚴重。因此 O3?TEOS 基的亞常壓化學汽相沉積 (SACVD)工藝再次提出被用于溝槽填充,由于它可以實現保形生 長,所以具有很強的填充能力(深寬比>10)。但是由于SACVD是一 種熱反應過程,所以傳統的SACVD生長速度都比較慢,美國應用材料公司AMAT的HARP(High Aspect Ratio Process)采用TEOS ramp-up技術,可以在保證填充能力的條件下,獲得較快的生長速度,這使得 SACVD代替HDP成為可能。而且隨著器件尺寸的減小,器件對等離子造成的損傷越來越敏感,SACVD由于是一種純熱過程,所以在45nm以后它比HDP有更多的優勢。

目前主要用于STI與PMD絕緣介質的填充。STI過程因為沒有溫度限制,所以可以通過高溫540℃獲得高質量高填充能力的薄膜,而 PMD由于有使用溫度限制,一般采用400℃沉積溫度。

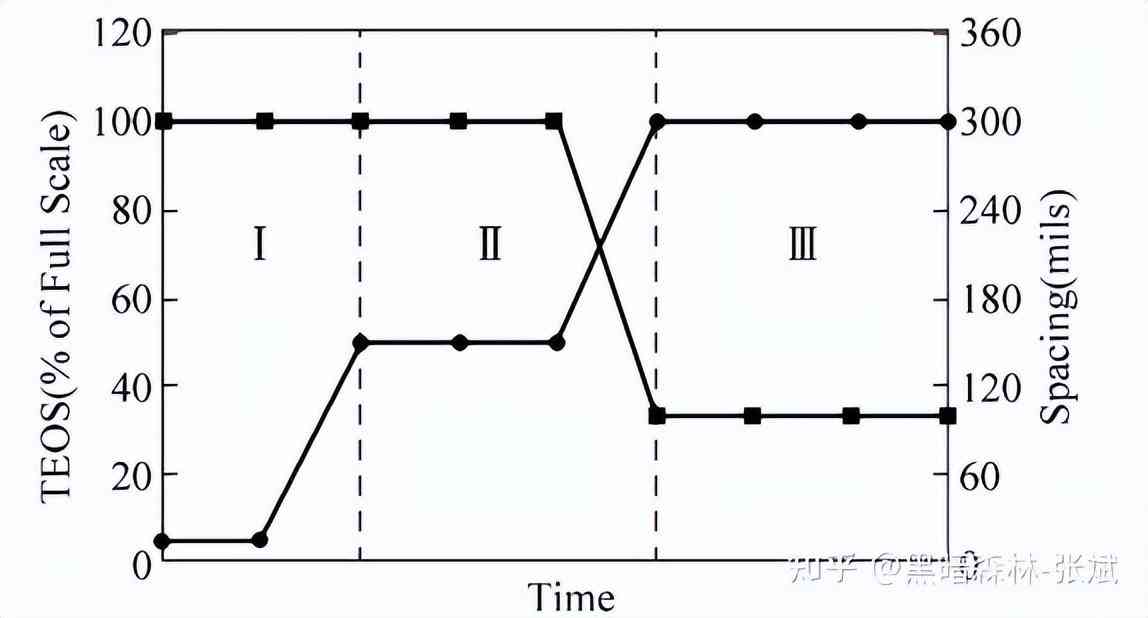

由于SACVD是一種熱反應過程,一般來講,低的沉積速度和高的 O3?TEOS 比值將獲得較高的填充能力。AMAT的HARP采用三步沉積法,通過調節 O3/TEOS 比例獲得較好的填充效果同時提高沉積速率 (見圖4.20):

步:是TEOS ramp up的過程,在沉積的起始階段, 保持非常高的 O3/TEOS 比例,以較慢的速度得到非常薄的成核層;

第二步:在較低的速度下保證填滿整個STI溝槽間隙。因此,把步與第 二步中的 O3/TEOS 比值設計得很高。

第三步:繼續提高反應中TEOS的流量,從而得到更高的沉積速率

圖4.20 HARP沉積中TEOS,spacing隨時間的變化

2.SACVD填充對溝槽輪廓的要求

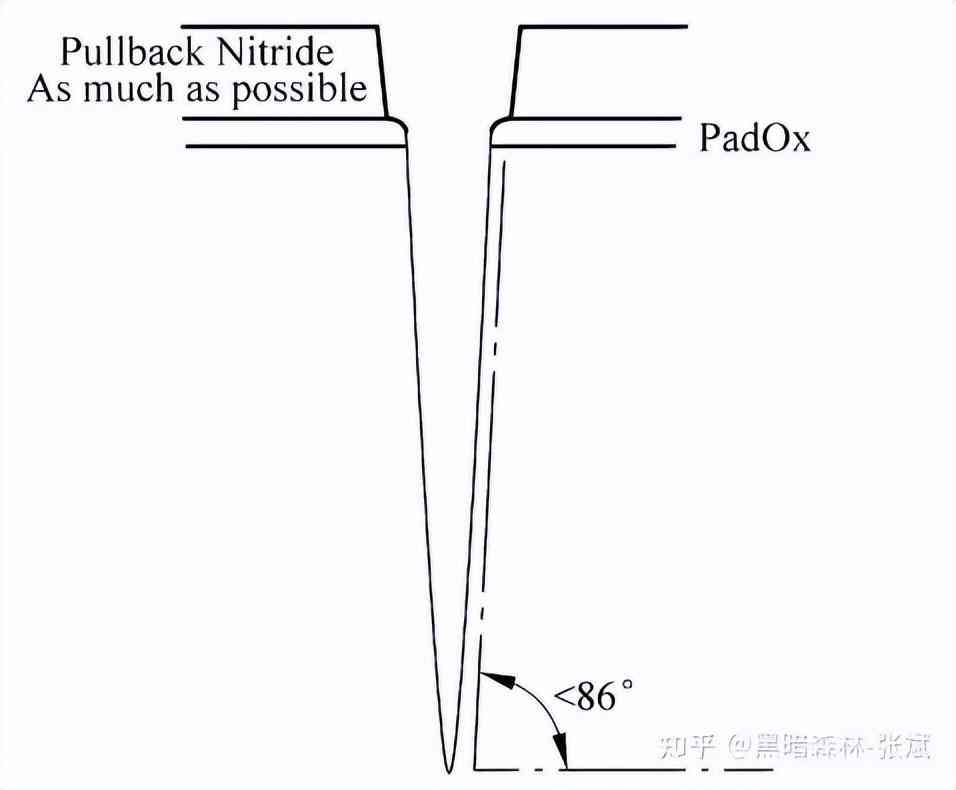

然而,HARP工藝的填充能力不僅受沉積中 O3/TEOS 比值的影響,更受到溝槽輪廓的強烈影響。以STI為例,SACVD沉積的保形性很高,所以HARP工藝主要采用坡度≤86°的V形溝槽形貌,保證STI溝槽的上端處于開口狀態,以完成自底向上的填充(見圖4.21)。

V形 STI可以很容易獲得良好的HARP填充效果。而U形的或凹角溝槽形貌會導致在STI被HARP薄膜填滿之前,STI溝槽的上端邊角早就被堵塞了,結果就會在溝槽內部形成鎖眼或裂縫。在處理U形或凹角STI形貌時,不存在一種能夠克服填充問題的簡便方法。很難通過HARP工藝 的一些改進來減輕U形或凹角溝槽形貌中的鎖眼(keyhole)。

圖4.21 用于HARP填充的理想溝槽形貌

3.SACVD沉積后的高溫退火

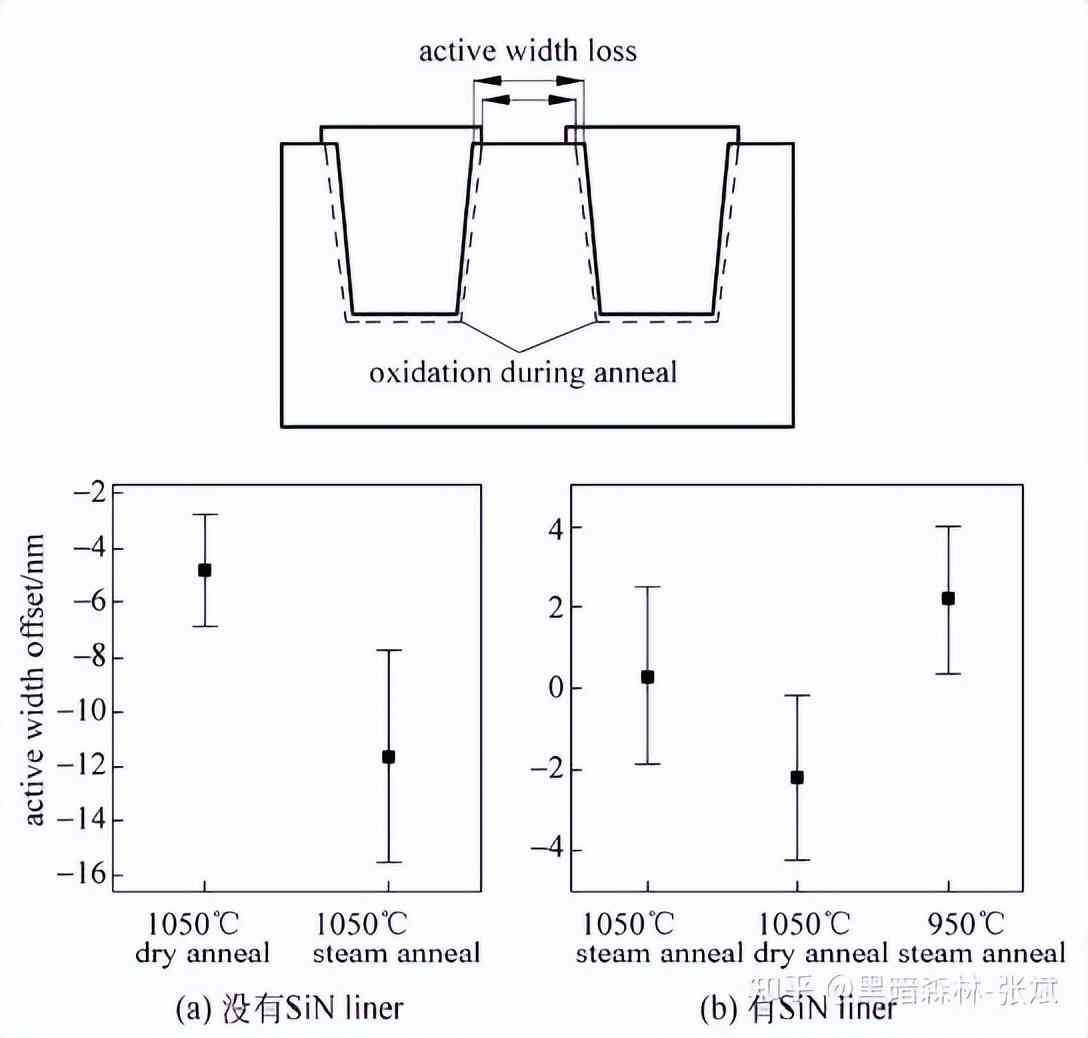

由于SACVD形成的SiO2 薄膜質量較差,所以在用于淺溝槽隔離時,在薄膜沉積完成后需要進行高溫的退火以提高薄膜的密度和吸潮性。目前退火主要包括:水蒸氣退火+N2 干法退火或N2 干法退火。在高溫退火的過程中,由于薄膜中存在氧(薄膜中殘存的或吸潮形成的O-H鍵),溝槽間的有源區會被進一步氧化而使得有源區面積損失;而水蒸氣退火更會使得活性Si面積損耗得更加嚴重。可以通過降低蒸氣退火的溫度或/和減少退火時間來減輕這個問題(見圖4.22)。

通過在STI溝槽側壁上插入SiN襯墊也可以預防損失,同時退火條件對 HARP填充能力也有一些影響。由于在干法退火后HARP薄膜大量收縮,所以有時在溝槽內部可以發現裂縫。與此相反,蒸氣退火可使 HARP收縮減少,從而獲得更好的填充效果。

圖4.22 高溫退火造成的活性硅的損耗

4.SACVD的應力

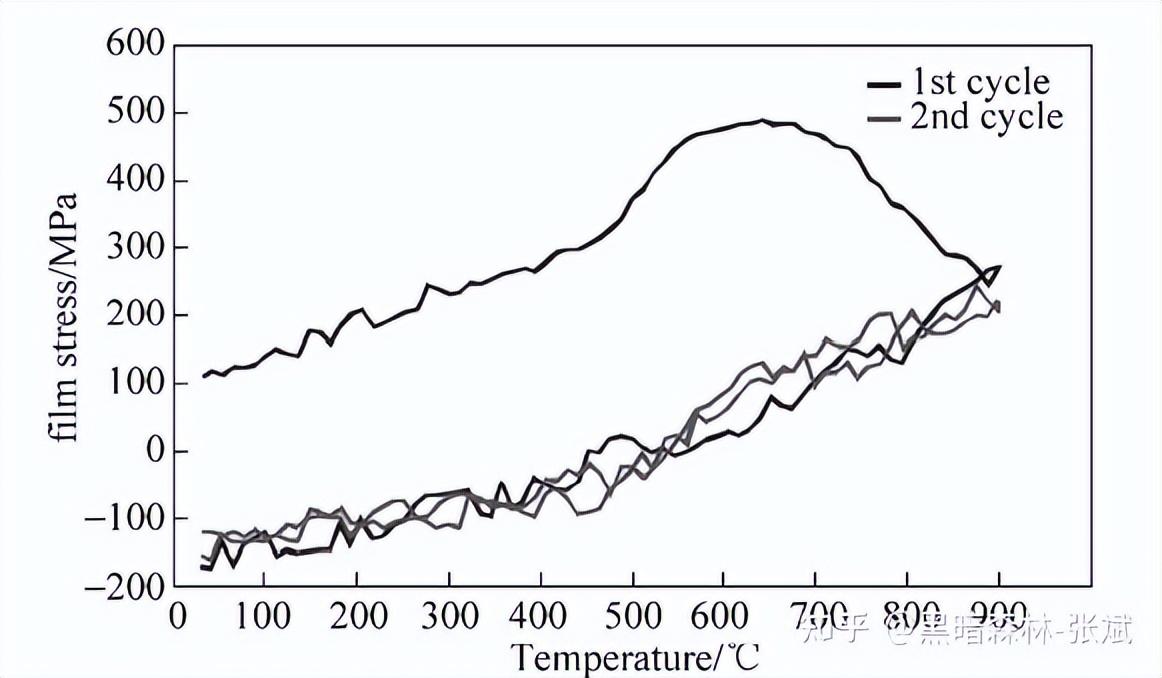

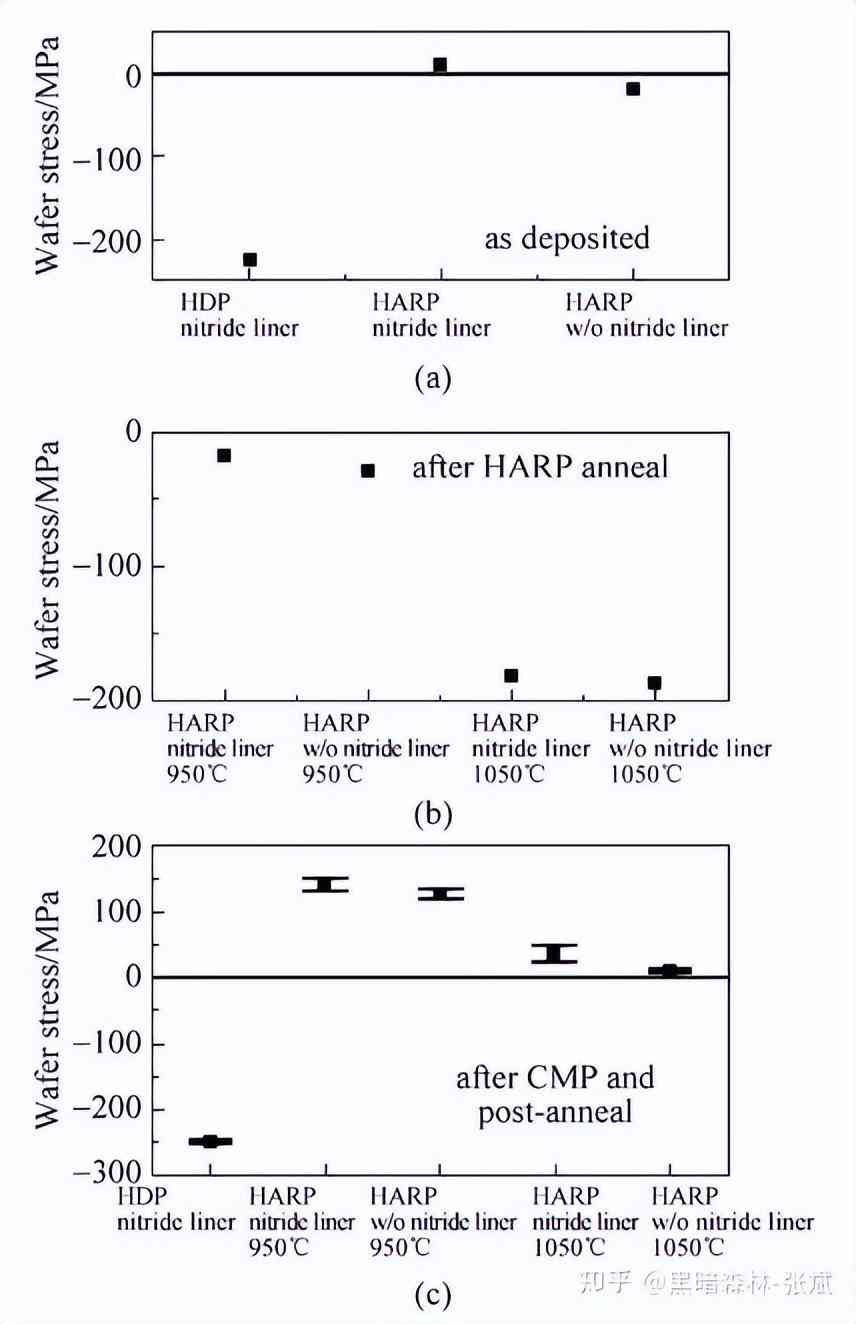

與具有壓縮薄膜應力的HDP不同,空白片沉積的HARP薄膜具有拉伸應力,經過高溫退火后,應力由拉伸轉為壓縮(見圖4.23)。但是對于圖形化的硅片,AMAT通過測定圖形化后硅片的彎曲程度,分別得到薄膜沉積后,退火后以及化學機械拋光后的硅片所受應力狀態,如圖4.24所示。沉積后與退火后結果與空白片結果類似,但是機械拋光后HDP會產生一個非常高的壓應力,但是HARP會對有源區產生拉應力,而且退火溫度也會對拉應力大小產生影響。

圖4.23 540℃ HARP空白片的薄膜應力-溫度曲線

圖4.24 圖形化硅片在不同條件下的應力

由HARP STI引起的拉伸應變可能是由兩方面的原因造成的。對該應力的回滯研究(見圖4.23)表明當退火溫度上升時,HARP薄膜應力將變得更加抗延伸,這將給活性Si帶來拉伸應變。即使冷卻后HARP薄 膜壓縮在一起時,這種張力應變仍然被記憶并保留在Si中。其次, HARP薄膜將在退火后收縮,但HDP薄膜不會。退火后HARP薄膜被限 制在溝槽中進行收縮,為Si提供了另一種強大的拉伸應變,這也進一步增強了NFET和PFET的載流子移動性,尤其是窄寬度晶體管器件。這也是采用HARP代替HDP的另一優勢。

5.SACVD薄膜生長的選擇性

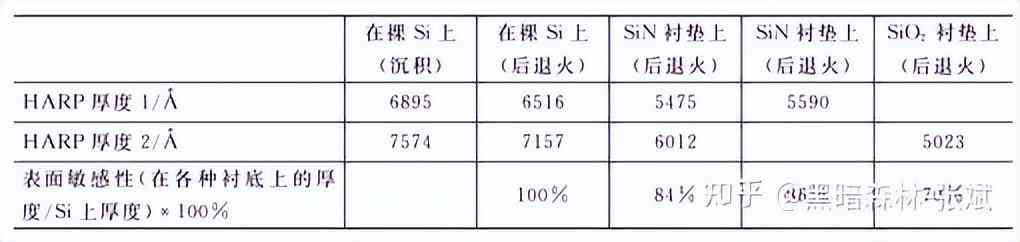

像所有其他SACVD O3?TEOS 工藝一樣 ,HARP沉積工藝也對襯底材料表現出了很高的敏感性。如表4.7所示,HARP在 SiO2 上比 在SiN上的沉積速率慢。這種敏感性與溫度、 O3/TEOS 比例以及壓力有非常強的關系,所以當評價HARP在CMP的溝槽中的loading時, HARP的表面敏感性也需要被考慮在內。

表4.7 HARP對不同襯底的表面敏感性

Qimonda等公司報道了利用SATEOS對襯底的敏感性,實現了薄膜在溝槽中選擇性生長,從而得到從下到上的填充效果。但是具體通過什么處理以及采用什么樣的條件,并沒有詳細的報道。

隨著器件尺寸的繼續減小,seam對填充的影響會越來越大,應用材料公司在HARP系統中引入 H2O 將是32nm或22nm的發展方向,另外通過刻蝕對HARP沉積中的輪廓進行修正也變得越來越重要。

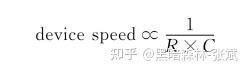

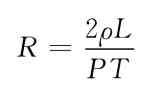

在超大規模集成電路工藝中,有著極好熱穩定性、抗濕性的二氧化硅一直是金屬互連線路間使用的主要絕緣材料,金屬鋁則是芯片中電路互連導線的主要材料。每一個芯片可以容納不同的邏輯電路層數,叫做互連層數。層數越多,芯片占據的面積就越小,成本越低, 但同時也要面對更多的技術問題。例如,不同的電路層需要用導線連接起來,為了降低導線的電阻(R 值)。隨著半導體技術的進步,晶體管尺寸不斷縮小,電路也愈來愈密集,也就是相對于元件的微型化及集成度地增加,電路中導體連線數目不斷地增多,導致工作時脈跟著變快,由金屬連接線造成的電阻電容延遲現象(RC delay),影響到元件的操作速度。在130nm及更先進的技術中成為電路中信號傳輸 速度受限的主要因素。

電路信號傳輸速度取決于寄生電阻(parasitic resistance,R )與及寄生電容(parasitic capacitance,C )二者乘積,當中寄生電阻問題來自于線路的電阻性,因此必須借助低電阻、高傳導線路材質,而IBM提出銅線路制程,就是利用銅取代過去鋁制線路,銅比鋁有更高的傳 (4-2) 導性、更低的電阻,可以解決寄生電阻問題。

因此,在降低導線電阻方面,由于金屬銅具有高熔點、低電阻系數及高抗電子遷移的能力, 已被廣泛地應用于連線架構中來取代金屬鋁作為導體連線的材料。另 一方面,在降低寄生電容方面,由于工藝上和導線電阻的限制,使得我們無法考慮借助幾何上的改變來降低寄生電容值。因此,具有低介 電常數(低k )的材料便被不斷地發展。

由于寄生電容C正比于電路層隔絕介質的介電常數k ,若使用低k 值材料(k <3)作為不同電路層的隔絕介質,問題便迎刃而解了。隨著互連中導線的電阻(R )和電容(C )所產生的寄生效應越來越明顯,低介電常數材料替代傳統絕緣材料二氧化硅也就成為集成電路工藝發展的又一必然選擇。

(4-2)

式中,R 是連接導線的電阻,其中一些常見金屬導體的電阻(單位 μΩ·cm)如下:

W/Al合金的電阻是4Al合金的電阻是3Cu電阻是1.7C 與絕緣體(insulator)的介電常數相關,列舉一些常見絕緣材料的介電常數:

SiO2 的介電常數是4fluorine silicon glass的介電常數是3.5black diamond的介電常數是3互連中導線的電阻(R )可以用下面的公式計算

(4-3)

式中,

ρ 是導線的電阻率;

L 是導線的長度;

P 是導線的寬度;

T 是導線厚度。

從式(4-3)中可以看出,導線的寬度P與電阻成反比。隨著晶體管尺寸不斷縮小,電路也愈來愈密集,相應地會減小導線的寬度P , 在一定程度上會增加R 值。

互連中導線的電容(C )是在金屬之間的寄生電容(見圖 4.25),可以用下面的公式計算

(4-4)

圖4.25 金屬之間的寄生電容

式中,k 是材料的介電常數,ε0 是真空介電常數。 合并式(4-3)和式(4-4)可得

(4-5)

從式(4-5)可知,RC ∝k ,圖4.26表示RC delay隨著器件尺寸的減小 而增加(在沒有使用新材料的條件下)。

圖4.26 RC delay是隨著器件尺寸的減小而增加(沒有使用新材料的條件下)的

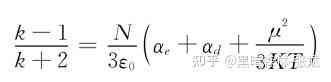

材料的介電常數k 與真空介電常數之間的關系為

(4-6)

式中,

k 是材料的介電常數;

ε0 是真空介電常數;

N 是每立方米中的 分子數;

αe 是電子云的極化率;

αd 是原子核的變形率;

μ 是永久電偶極矩;

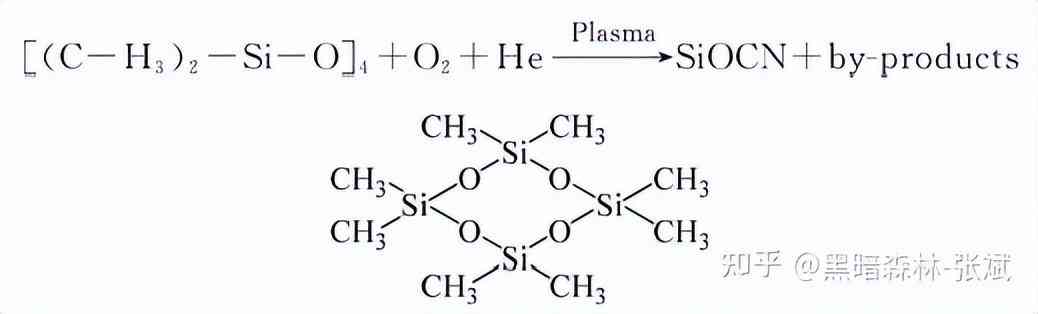

目前,業界普遍選擇的低介電常數是black diamond(SiCON)薄 膜材料,它的k 值可以控制在2.7~3.0,且能夠滿足130nm、90nm、 65nm和45nm技術要求。 八甲基環化四硅氧烷(OMCTS)是沉積SiCON薄膜的前驅物,八甲基環化四硅氧烷在常溫條件下是液體,沸點是175~176℃,分子量 是296.62。通過載氣He把OMCTS輸入到反應腔中,其具體反應如下

八甲基環化四硅氧烷的分子式

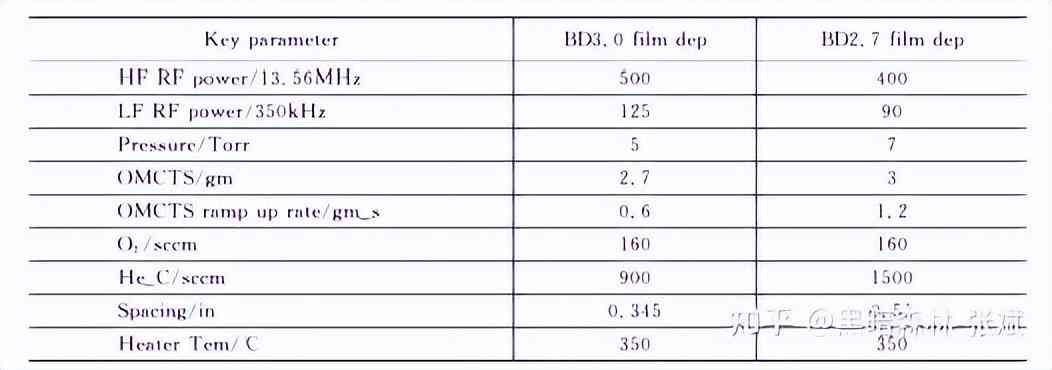

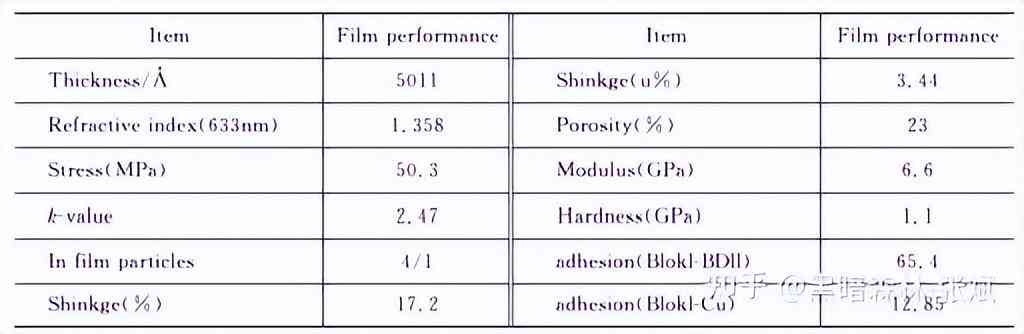

另外,表4.8指示在沉積k 值為3.0和2.7低介電常數材料(見圖 4.27)的一些關鍵參數的差異,表4.9指示k 值為3.0和2.7低介電常數材 料的性質差異

表4.8 BD3.0 and BD2.7 film deposition

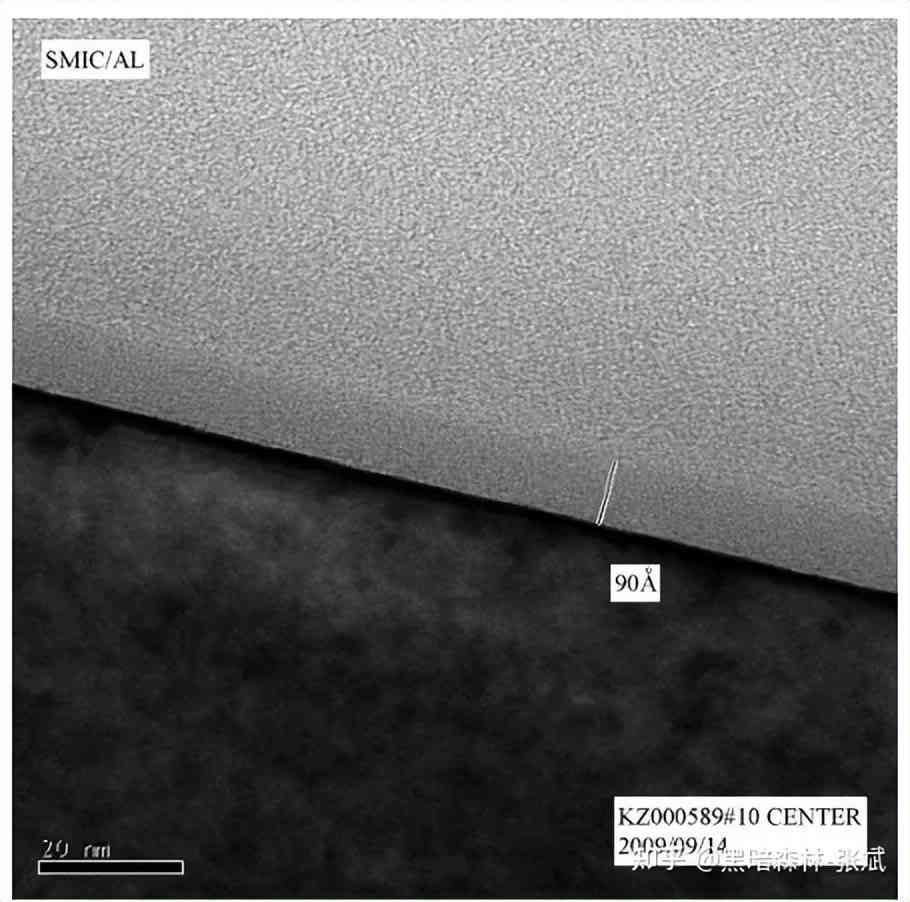

圖4.27 介電常數為2.7的薄膜的TEM照片

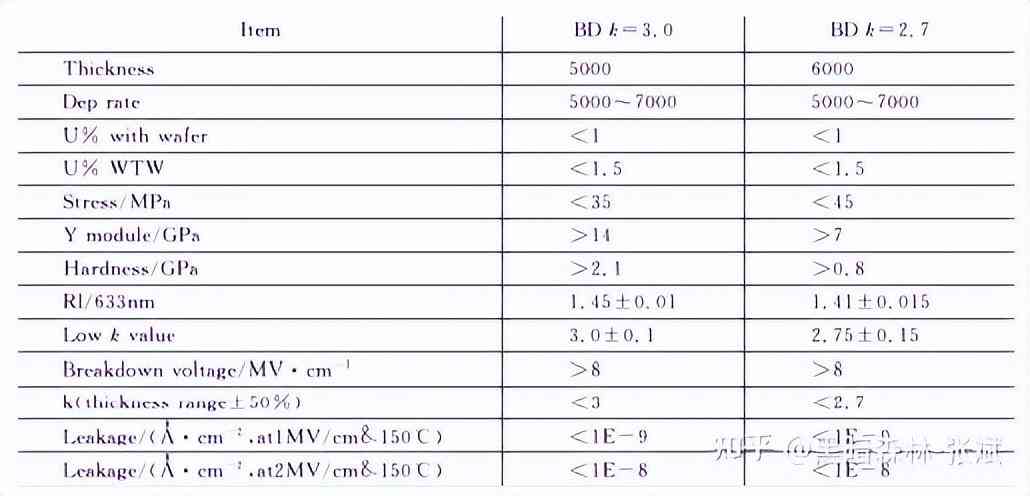

表4.9 Film peculiarity of BD3.0 and BD2.7

低介電常數層間絕緣膜(低k材料)的用途為減小布線間的電 容。布線間的電容與絕緣膜的相對介電常數和布線的橫截面積成正 比,與布線間隔成反比。伴隨加工技術的微細化,布線橫截面積和布 線間隔越來越小,結果導致布線間電容的增加。因此,為了在推進加 工技術微細化的同時又不至于影響到信號傳輸速度,必須導入低k 材 料以減小線間電容,從而可以很好地減少電信號傳播時由于電路本身 的阻抗和容抗延遲所帶來的信號衰減。

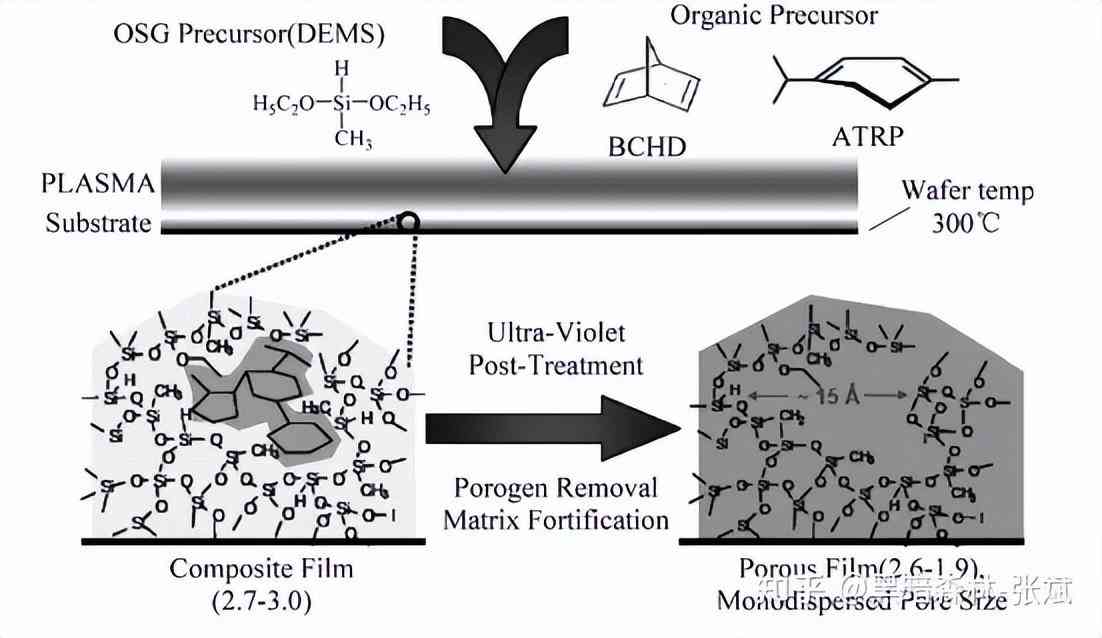

為了獲得介電常數小于或等于2.5的低k 材料,研究出一種通過在 有機硅化合物玻璃中對低k 材料進行紫外光熱(ultraviolet radiation) 處理,圖4.28表示超低介電常數(<2.5)的多孔薄膜的沉積工藝。圖 4.29是沉積超低介電常數(<2.5)的多孔薄膜的設備,圖4.30是超低 介電常數(<2.5)的多孔薄膜的照片。表4.10表示超低介電常數(< 2.5)的多孔薄膜的特性。

圖4.28 超低介電常數(<2.5)的多孔薄膜的沉積工藝

圖4.29 沉積超低介電常數(<2.5)的多孔薄膜的設備

圖4.30 沉積超低介電常數(<2.5)的多孔薄膜的TEM照片

表4.10 超低介電常數的多孔薄膜的特性

在65nm、90nm和130nm技術所用的copper barrier and etching stop layer介電常數材料的k 值是5.1左右。

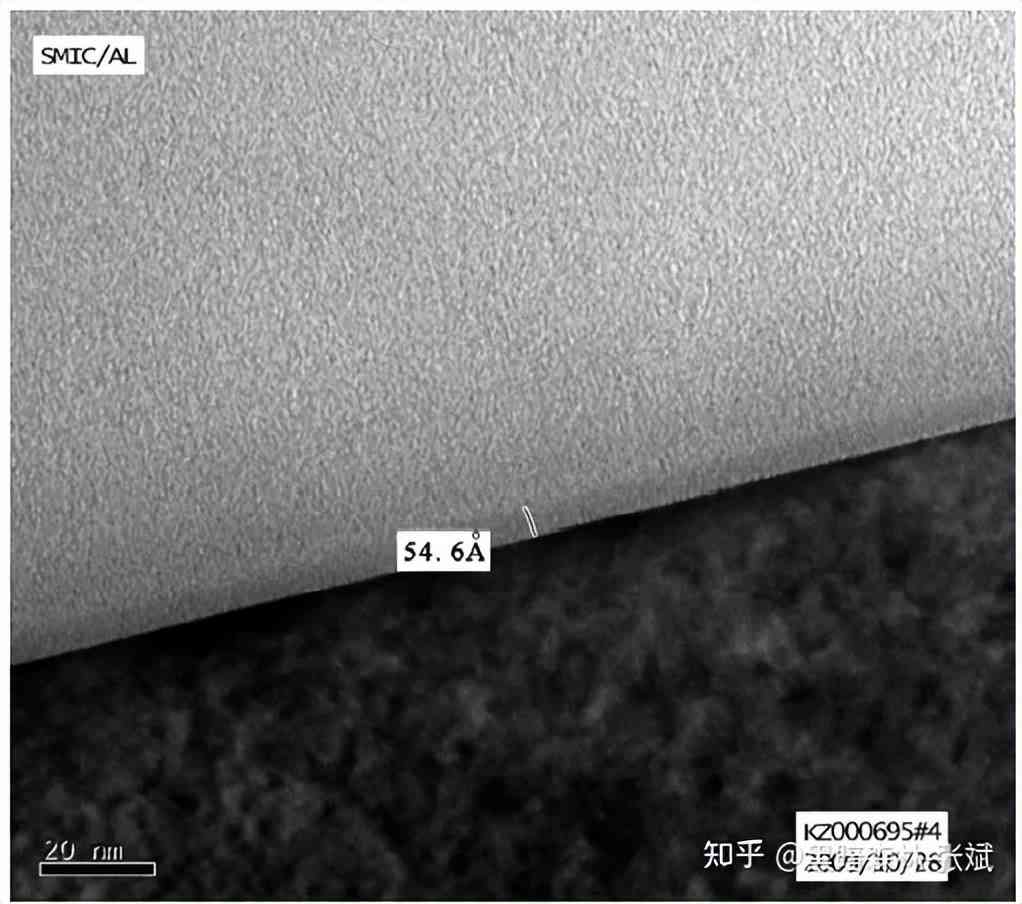

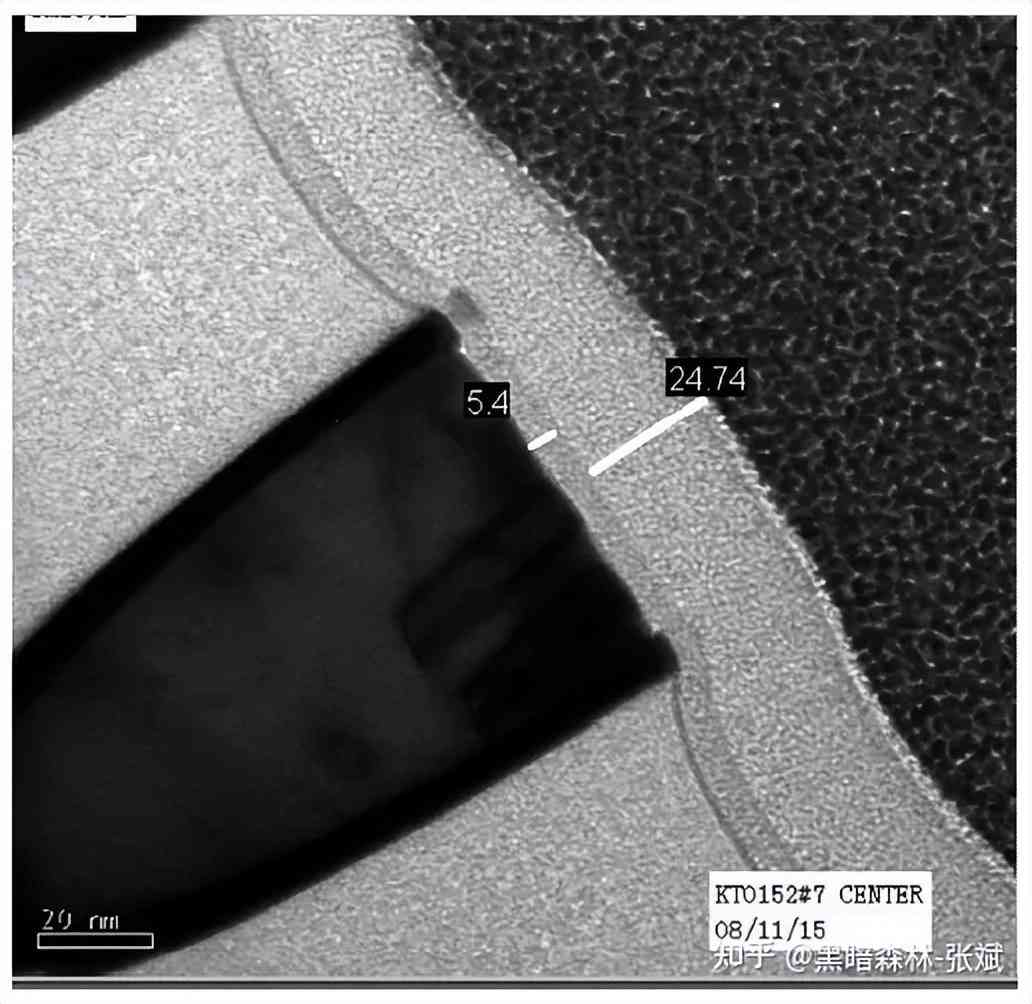

對于45nm和32nm技術,為了減少介電常數材料的k 值對RC delay 的影響,采用bilayer etching stop layer and copper barrier介電常數材 料。層仍然采用k 值是5.1薄膜材料,具有好的copper barrier效 果,第二層采用k 值是3.8薄膜材料,在一定程度上可以減少器件RC delay。圖4.31表示bilayer etching stop layer and copper barrier介電常數 材料的TEM照片,層的厚度大約為50?,第二層的厚度大約為 250?。

圖4.31 刻蝕停止層與銅阻擋層介電常數材料的TEM照片

為深入學習貫徹落實黨的二十大和二十屆一中...

Burberry是一個具有濃厚英倫風的著...

高奢月子中心圣貝拉(SAINT BELL...

近年來,國際政治經濟環境復雜多變,不確定...

如果有這樣一...

近日上海智美顏和以60后--90后的不同...

名品導購網(www.cctv-ss.com)ICP證號: 蘇ICP備2023000612號-5 網站版權所有:無錫錫游互動網絡科技有限公司

CopyRight 2005-2023 版權所有,未經授權,禁止復制轉載。郵箱:mpdaogou_admin@163.com